K-WANG

GE VME-3122A High Performance 16 Bit Analog to Digital Converter (ADC)

GE VME-3122A High Performance 16 Bit Analog to Digital Converter (ADC)

Basic Information

Product Name: VME-3122A High Performance 16 Bit Analog to Digital Converter (ADC) Board

Production company: GE Fanuc Intelligent Platforms

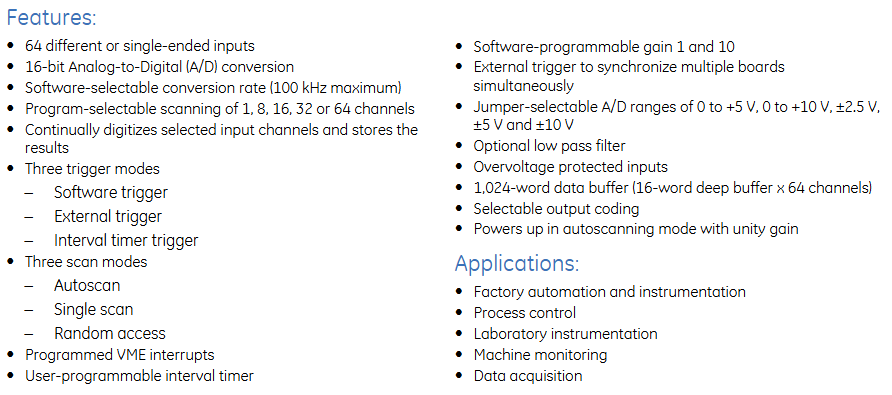

Main features

64 different or single ended inputs

16 bit analog-to-digital (A/D) conversion

Software selectable conversion rate (maximum 100kHz)

Programmable options for scanning channels 1, 8, 16, 32, or 64

Continuously digitize the selected input channel and store the results

Three triggering modes: software triggering, external triggering, and interval timer triggering

Three scanning modes: automatic scanning, single scan, and random access

Programmable VME interrupt

User programmable interval timer

Software programmable gains 1 and 10

External triggering can synchronize multiple boards simultaneously

Jumper selectable A/D range: 0 to+5V, 0 to+10V, ± 2.5V, ± 5V, and ± 10V

Optional low-pass filter

Over voltage protect

1024 word data buffer (16 word deep buffer x 64 channels)

Optional output encoding

When powered on, it is in automatic scanning mode with a gain of 1

Application Fields

Factory automation and instrumentation

process control

laboratory instruments

Machine monitoring

data acquisition

Ordering Options

Option Description

A (input filter option) 0=no filter; 1=10Hz(-3dB); 2=50Hz(-3dB); 3=100Hz(-3dB); 4=500Hz(-3dB)

B (channel quantity option) 0=64 channels high performance; 1=32 channels high performance; 2=16 channels high performance

C (input option) 0=differential analog input channel with 96 pin non latch connector; 1=Single ended analog input channel with 96 pin non latch connector; 2=Differential analog input channel with 64 pin latch connector; 3=Single ended analog input channel with 64 pin latch connector

DE 0 (reserved for future options)

F (Special Sales Order) 0=Standard VME front panel without conforming coating; 1=Reserved; 2=Standard VME front panel with conforming coating

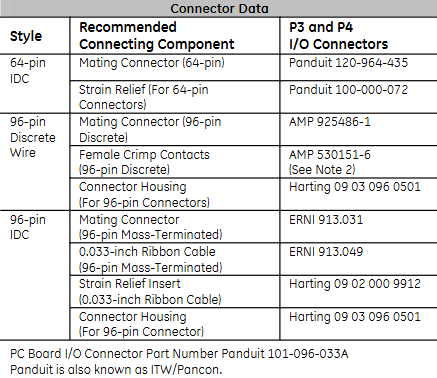

Connector data

Recommended style for connecting components P3 and P4 I/O connectors

64 pin IDC mating connector (64 pin) Panduit 120-964-435

Strain relief (applicable to 64 pin connectors) Panduit 100-000-072

96 pin discrete mating connector (96 pin discrete) AMP 925486-1

Female crimping contact (96 pin discrete) AMP 530151-6

Connector housing (suitable for 96 pin connectors) Harting 09 03 096 0501

96 pin IDC mating connector (96 pin large-scale termination) ERNI 913.031

0.033-inch ribbon cable (96 pin large-scale termination) ERNI 913.049

Strain relief insert (0.033-inch ribbon cable) Harting 09 02 000 9912

Connector housing (suitable for 96 pin connectors) Harting 09 03 096 0501

PC board I/O connector part number Panduit 101-096-033A

Functional characteristics

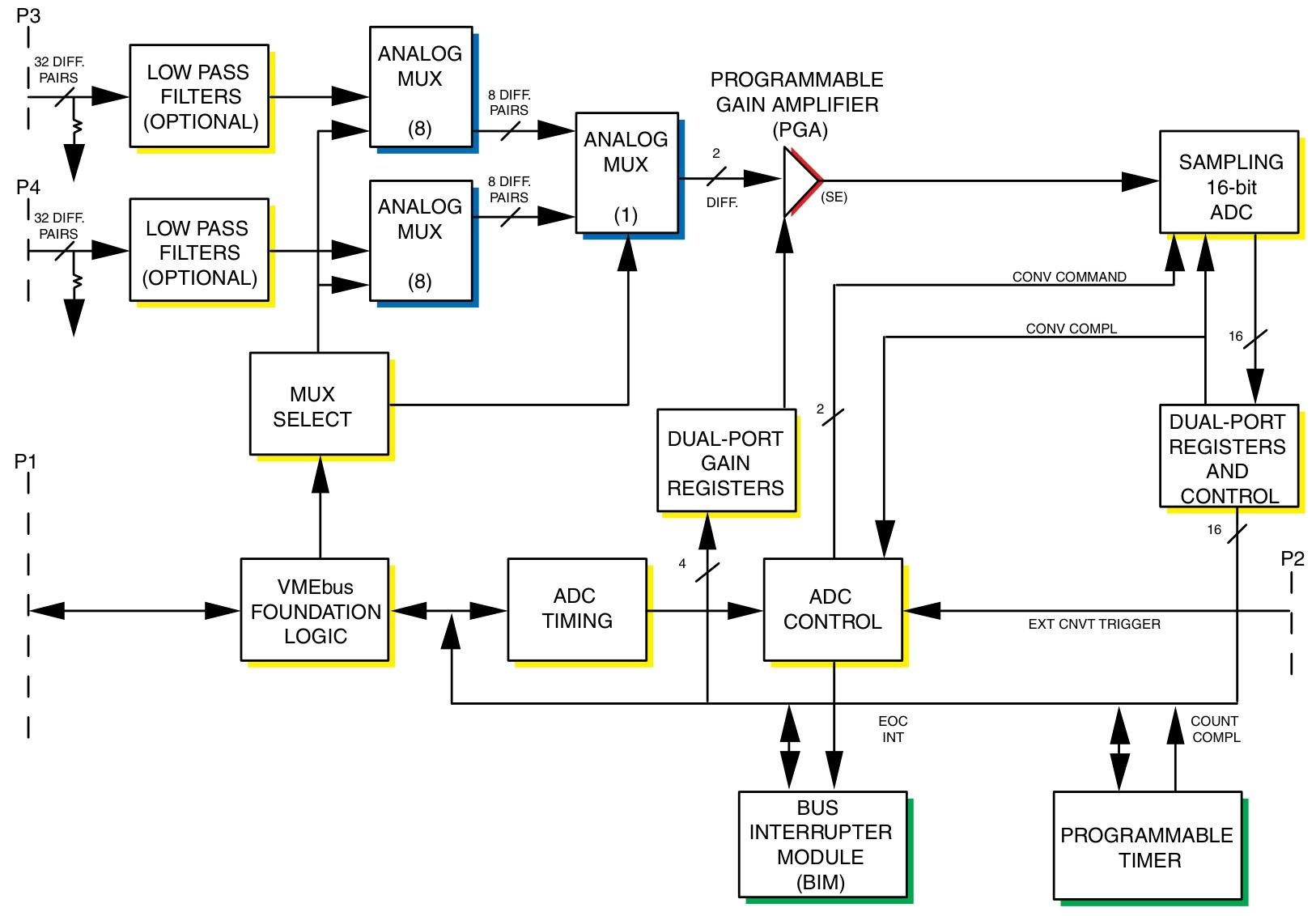

1. Working mode

MODE

Software trigger: Start the selected scanning mode by writing the software trigger address

External trigger: The external trigger received on the P2 connector initiates the selected scanning mode

Interval timer trigger: Start the selected scanning mode each time the programmed time interval expires

SCAN

Automatic scanning: default scanning mode, all active channels are scanned continuously in order

Single scan: Start a single data burst (scanning all selected channels) from the selected trigger mode, stop and wait for another trigger after scanning all selected channels

Random access: Each time the selected trigger mode is enabled, a single channel can be selected, digitized, and stored

Channel automatic gain: The unique gain code for each channel is loaded from VME into the gain buffer, and the allocated code is retrieved in real-time from the buffer during each channel acquisition

Synchronization: A single scan or burst can be initiated by an external TTL trigger through the P2 connector (external trigger) or a local trigger through the control and status register (CSR) (software trigger), and any event will generate a P2 trigger output, which can be used to synchronize up to 15 cards

2. VME related characteristics

VME access: The response to the address modifier can be selected as A32, A24, or A16 address space through jumper wires; Monitoring or user privileges, or both

VMEbus compliance: Compliant with VMEbus specifications ANSI/IEEE STD 1014-1987, IEC 821 and 297, with 6U external dimensions

VME interrupt: An interrupt request can be generated at the end or in the middle of a buffer scan, or it can be initiated after collecting a specific number of samples (1 to 65535), and the response vector is controlled through the interrupt vector register

Data ready flag: When the data buffer is full (end of scan) or half full (middle of scan), the data ready flag in CSR is set

Interval timer: Programmable interval timer provides a time interval of up to 687 seconds

3. Reset operation

Board reset response system reset or writing software reset address

The reset operation automatically establishes the following default conditions: automatic scanning mode, 64 channel block size, 64 channel data buffer, channel gain=x1, 100kHz conversion rate

ADC will undergo a calibration cycle under any reset condition, which takes 41ms after the reset operation is initiated

4. Other functions

PGA: Channel gains of x1 and x10 can be selected through a programmable gain amplifier (PGA). The PGA gain can be configured through software as a single gain for all channels, or real-time control can be used to assign unique gains to each channel

Panel indicator: The front panel LED controlled by the program is powered on during the reset period and turned off through CSR

Board Identification: The Board Identification Register (BIR) contains the VME-3122A identification code

Input characteristics

Number of input channels: 64, 32, or 16 differential or single ended channels

Full range A/D range: ± 2.5V, ± 5V, ± 10V, 0 to+5V, 0 to+10V, jumper optional

Channel gain: Software configuration is x1 or x10

Full range input range

Gain=1: ± 2.5V to ± 10V (bipolar); 0 to+5V, 0 to+10V (unipolar)

Gain=10: ± 250mV to ± 1V (bipolar); 0 to+0.5V, 0 to 1V (unipolar)

Accuracy (% of FSR): There are different values for different ranges and gains, based on the average of 1000 samples

Stability: Temperature drift, per degree Celsius=± 25PPM (ADC reading) plus ± 5PPM (ADC range) plus ± 2.5 µ V

Input noise: (0.4+0.3/G) mV, where G=PGA gain (noise is independent of filter options)

Input bias current (typical/maximum): 50/120nA

Input impedance (minimum): Different DC differential, DC common mode, AC differential, and AC common mode impedances when the power is turned on and off

Channel crosstalk (DC to 1kHz): 80dB between adjacent channels within ± 10V range; 70dB between adjacent channels within ± 2.5V range

Common mode voltage range: (IVCM |+| VIN |. G) ≤ 10V, where VCM=common mode voltage, VIN=input voltage, G=gain

Common mode rejection: From DC to 60Hz, when the 350 Ω source is unbalanced, the minimum common mode rejection for gain 1 is 68dB, typical 80dB; the minimum common mode rejection for gain 10 is 76dB, typical 89dB; the minimum common mode rejection for+5V and ± 2.5V ranges is 66dB, which can be adjusted on-site to achieve the same common mode rejection as gain 1

Overvoltage protection: ± 35V (continuous) power on/off; ± 80V (transient, maximum 1s)

Input filter: Optional low-pass single pole filter with different -3dB values at different frequencies, frequency doubling in single ended (pseudo differential) applications, cut-off frequency tolerance of ± 25%, unfiltered input bandwidth (20Vp-p) typically 40kHz

Common mode/floating input protection: Both sides of each input are grounded through a 22M Ω resistor

Transmission characteristics

Resolution: 16 bits

Input sampling: order, starting from channel 00

Input transfer function:

E IN=E LO+E FSR × 65536N ADC, where E IN=input voltage, E LO=lower end of input range, E FSR=full-scale input range, N ADC=A/D converter reading

A/D conversion rate: 381 to 100kSPS

Channel sampling rate (maximum): 100kSPS (100kSPS ÷ number of channels in the scan block, minimum 1 channel)

Time interval: 305 µ s to 687s

Data encoding: programmable to choose binary complement or direct/offset binary

Data buffer storage

Buffer size: 16 to 1024 consecutive 16 bit data words, program controlled

Block size: 1, 8, 16, 32 or 64 channels, program controlled

Access time: maximum 600ns during non scanning; typical 600ns during scanning, maximum 1.2 µ s (maximum access time in scanning mode only occurs when VME access occurs within the ADC sampling window)

VME access: D8 to or D16

Availability: Can be accessed from VME at any time, buffer and block sizes are controlled through configuration control registers (CCR)

Physical/Environmental Specifications

Size: 6U (4HP) single slot Eurocard shape

Height: 9.2 inches (233.4mm)

Depth: 6.3 inches (160mm)

Thickness: 0.8 inches (20.3mm)

Power requirement: 3.0A at+5VDC (maximum)

Airflow: Forced air cooling is required

Temperature: Operating temperature 0 to+65 ° C; Storage temperature -40 to+85 ° C

Altitude: Working at 0-10000 feet (3000m); Storage 0-40000 feet (12000m)

Humidity: Working relative humidity 0% to 80%, no condensation

Input connectors (P3, P4): can be ordered as 96 pin DIN non latch or 64 pin DIN latch. The center row of the 96 pin non latch connector is grounded, while the center row of the 64 pin latch connector is not grounded. When using the 64 pin latch connector in differential mode, users can provide grounding on the front panel jumpers E1 and E2, which will result in channels 31 and 63 being configured as single ended

UIOC support

In UIOC, VME-3122A is used as a monitoring device. During initialization, UIOC programs VME-3122A to scan all 64 channels and sets the scanning mode to automatic scanning. Through UCLIO ™ Language, users can set programmable channel gains and command UIOC to retrieve data from any or all channels of VME-3122A. Through a menu driven calibration process, users can create and store channel gain and offset correction factors, which UIOC automatically uses to provide software gain and offset correction for each channel.

- YOKOGAWA

- Reliance

- ADVANCED

- SEW

- ProSoft

- WATLOW

- Kongsberg

- FANUC

- VSD

- DCS

- PLC

- man-machine

- Covid-19

- Energy and Gender

- Energy Access

- Renewable Integration

- Energy Subsidies

- Energy and Water

- Net zero emission

- Energy Security

- Critical Minerals

- A-B

- petroleum

- Mine scale

- Sewage treatment

- cement

- architecture

- Industrial information

- New energy

- Automobile market

- electricity

- Construction site

- HIMA

- ABB

- Rockwell

- Schneider Modicon

- Siemens

- xYCOM

- Yaskawa

- Woodward

- BOSCH Rexroth

- MOOG

- General Electric

- American NI

- Rolls-Royce

- CTI

- Honeywell

- EMERSON

- MAN

- GE

- TRICONEX

- Control Wave

- ALSTOM

- AMAT

- STUDER

- KONGSBERG

- MOTOROLA

- DANAHER MOTION

- Bentley

- Galil

- EATON

- MOLEX

- Triconex

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- KOLLMORGEN

- Beijer

- Endress+Hauser

- schneider

- Foxboro

- KB

- REXROTH

- YAMAHA

- Johnson

- Westinghouse

- WAGO

- TOSHIBA

- TEKTRONIX

- BENDER

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- XP POWER

- Baldor

- Meggitt

- SHINKAWA

- Other Brands

- other brands

- UniOP

- KUKA

- IBA

-

Metso XZB10025-011T12 - Moog Valve 9650962700

-

Metso XZB10025-010T12 - Moog Valve 9650965300

-

Metso-SP Transmitter Cable - Operating Unit with 10m Cable

-

Harkila Metso Hybrid - Hunting Jacket Willow Green

-

Metso ND8221/S1 - Neles Valve Positioner

-

Metso METSO10119 - ScreenCheck Component

-

Metso LK-2025 - Linkage Kit

-

Metso A416733 - IQweight External Air Gap Temperature Sensor

-

Metso RKC22MT - Automation Component

-

Metso A413281 - Automation Board

-

Metso LCP9HLY - Stainless Steel Enclosure

-

Metso NP704S/B1S1 - Pneumatic Positioner with I/P Converter

-

Metso BAH3 - Slurry Seal Type

-

Metso A413531-03 - PLC Module Chassis Rack

-

Metso P4610004 - MCAI Communicator Controller

-

Metso QN2AN03HDM - Quartz Valve Positioner Stonel

-

Metso RKW-352-XZ - Automation Component

-

Metso A4300081 - Kajaani LCD Display

-

Metso A428026 7B - Kajaani Rectifier Unit 1

-

Metso 202218 - Kajaani Sensor Power Supply SR 902660

-

Metso 9150 316SS CSTL - Jamesbury 150-2" BN50 Valve

-

Metso 81806 - IOP101 Module

-

Metso STOM000272 - Paper Bushing CR38

-

Metso 1975413 - Chain Hoist Links

-

Metso IMO G053-191597 - Minor Seal Kit

-

Metso VAL0087418 - Cylinder Valmet NTS6LV

-

Metso A413061 - DMU Board VPA 420355-4B

-

Metso P2620-80/25-100 - Automation Component

-

Metso VAL0035292 - Automation Component

-

Metso A413721 - Automation Component

-

Metso ST600 - Automation Component

-

Metso P4500001 - Automation Component

-

Metso SDBX/RA2 - CAT x KVM Extender

-

Metso D201126-DI8 - Digital Input Module

-

Metso D201189L - AI8H Analog Module

-

Metso NA004418 LK1016 - Wafersphere Actuator Mounting Bracket

-

Metso RKN172MTT - Repair Kit

-

Metso MM0311584 - Air Filter Kit RadialSeal

-

Metso 181517 - IOP301 Isolated Analog Input Module

-

Metso RAU3906506 - Automation Component

-

Metso 181208 - IOP332 Digital Input Module

-

Metso A413760 - AIF2C PCB Module

-

Metso 006 1089 36 - Shaft Bearing Seal

-

Metso A413046 - Automation Component

-

Metso VKJ650 - Automation Brake Component

-

Metso LK-1875 - Linkage Kit

-

Metso D201193L - FI4S24 Frequency Input Module

-

Metso D200533 - BIU82 Binary Input Module

-

Metso 500838-M1 - Impeller Pump Release Collar Assembly

-

Metso 2.00SB2ALUS19A - Pneumatic Cylinder 1.375 Stroke

-

Metso D201351 - RES Reserve Module

-

Metso A416100 - IQMoisture Spare Part Kit Halogen Lamp

-

Metso Slurry Pump - Back Liner

-

Metso 7088010042 - Bronze Lantern Ring

-

Metso IMC-101-M-SC - Industrial Media Converter

-

Voith S1-S1-CAM-ENCL - Metso Pump Cmare Housing & Bracket

-

Metso A4430726V1.1 - Kajaani Connection Box CI 4-9-10

-

Metso A413016 - NCU2 PLC Board

-

Metso D202213P - MBMT80 Base

-

Metso A413135 - AOU-4 Analog Output Board

-

Metso NP 724A - Pneumatic Valve Positioner

-

Metso A413246 - Automation Controller Module

-

Konaflex VKJ-650 - Disc Brake Set Pair

-

Metso WIN3096535D - Core Chuck

-

Metso D201380 - MBR Base with IBC & IPS

-

Metso D202213L - MBMT80 Base Module

-

Metso 181571 - IOP337 PLC Module

-

Metso MF0588336 - Main Hydraulic Filter

-

Metso 181504 - IOP303 RTD Input Module

-

Metso A413240 - PIC2 Board

-

Denver 566534PS - Case Liner Gland Side SRL Frame 2

-

Metso 181508 - IOP322 Digital Input Module 120V

-

Metso 181520 - IOP351 Relay Output Module Form A/B

-

Metso 181220 - IOP351 Relay Output Module

-

Metso A413150 - BOU 8 Binary Output Module

-

Metso 128400-M1 - Impeller

-

Metso D201379 - MBB Base with IBC & IPS

-

Metso 205181 - T/B MTD PRWSW Assembly

-

Metso QPX1C/K15 - Jamesbury Quadra-Powr X Actuator Valve

-

Harkila Metso Winter - Hunting Jacket Willow Green

-

Metso NE724A/A-L - Electro-Pneumatic Positioner

-

Metso PACP-100-80-31 916 - Automation Component

-

Metso 81814 - Automation Component

-

Metso ER-12-01-M-CT - Automation Board

-

Metso ELO24 - Automation Board

-

Metso A413000 - Valmet Neles CPU PLC Board

-

Metso XL-2213-0525 - Mainframe Bushing

-

Metso D100097 - ECR Extension Module

-

Metso 804511 - Filter Housing Assembly

-

Metso S420154 - Automation Rack Chassis

-

Metso M851232 - Automation Module

-

Metso D100532 02 - Automation Board

-

Neles QPX1C/M - Ball Valve with Quadra-Powr X Actuator

-

Metso 181535 - IOP322 Isolated Analog Output Module

-

Metso RKN-184-XTZ - Ball Valve Seat Repair Kit 4"

-

Metso N22022621 - Metal Plate

-

Metso 181560 - IOP341 Positioner Module

-

Metso LT 1213 S - Filter Service Kit for CAT C12 Engine

-

Aq-Matic 0032-99000 - Valve Diaphragm

-

Metso D200535 - BOU8 Output Board

-

Metso EDS-305-M-SC - Ethernet Switch

-

Metso 80424 - IOP110 Analog Output Module

-

Metso IOP351 - Relay Output Module Form A/B

-

Metso 181572 - IOP342 Module

-

Metso 1-1-2A3600TT - Ball Valve 1.5"

-

Metso A413154 - BOU8-4 Output Module

-

Metso A413140 - Valmet BIU 8 Board

-

Metso D201139 - IPS Power Supply type DDC7940

-

Metso PGH P411382-2000 - Metal Feed/Filtrate Hose

-

Valmet 503201404 - Automation Board

-

Metso 181507 - IOP331 Controller Module

-

Metso A413141 - BIU82 Binary Input Module

-

Metso KSD7447686 - Pneumatic Cylinder 5" Bore

-

Metso APL3003850 - Automation Component

-

Metso D201135L - Automation Controller

-

Metso A413125 - AIU8 Analog Input Module

-

Metso A413325 - IPU Power Unit

-

Metso 181573 - IOP346 PLC Module

-

Metso A413143 - BIU84 Binary Output Module Card

-

Metso A413152 - BOU82 Output Module

-

Metso PDP603 - Distributed Processing Unit 181555

-

Metso PDP601 - Distributed Processing Unit 181555

-

Metso A413040 - DCS Board DCU

-

Metso A413082 - CPU Processor Module

-

Valmet TI4W3 - Temperature Input Module

-

Valmet FI4S24 - Frequency Input Module

-

Metso 1064669615 - Fulcrum Bar

-

Valmet 181206 - IOP330 Digital Input Module

KONG JIANG

Add: Jimei North Road, Jimei District, Xiamen, Fujian, China

Tell:+86-15305925923