K-WANG

GE VMIPCI-5565 Ultrahigh Speed Fiber-Optic Reflective Memory with Interrupts

GE VMIPCI-5565 Ultrahigh Speed Fiber-Optic Reflective Memory with Interrupts

Product Overview

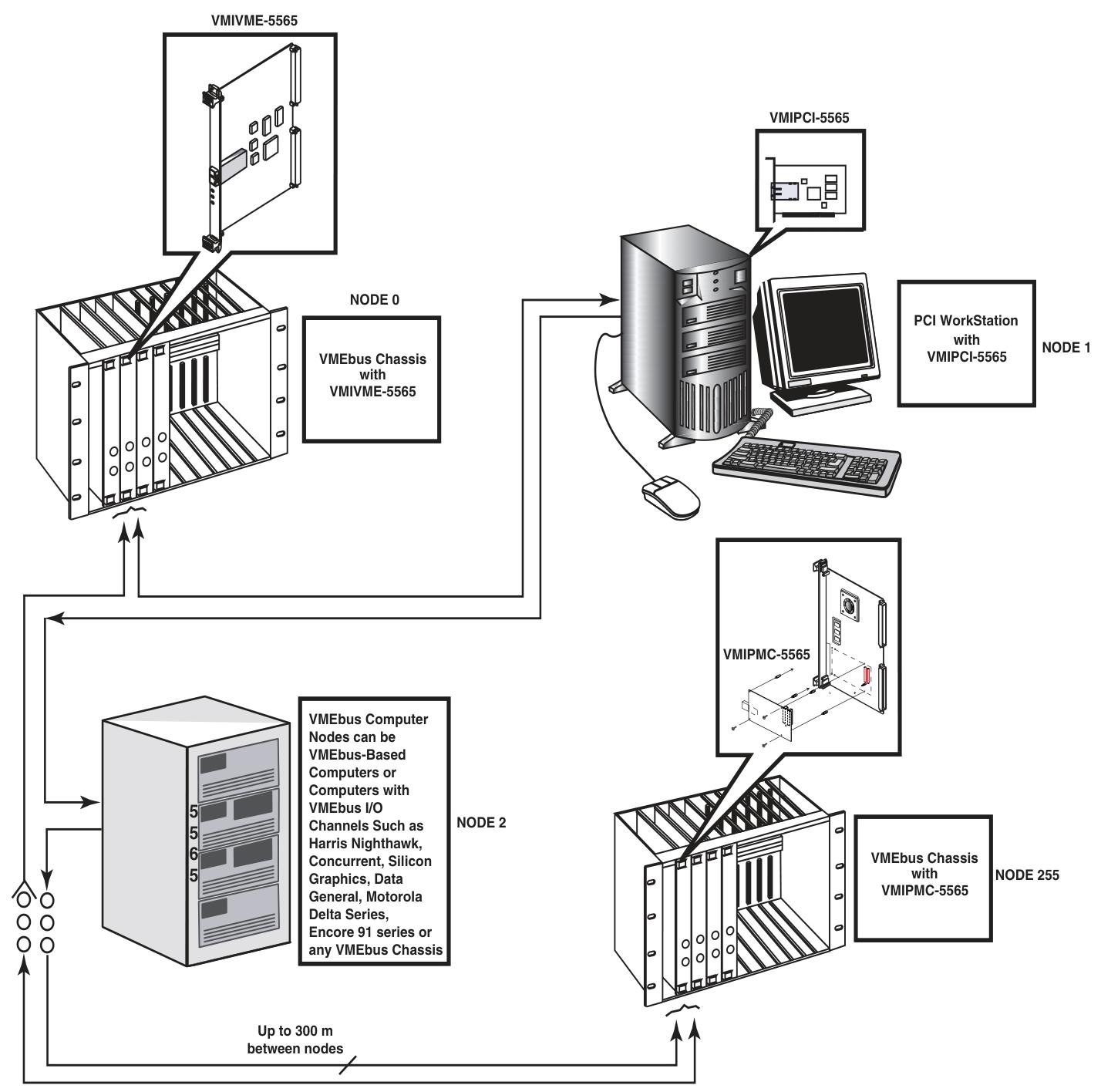

Basic information: VMIPCI-5565 is a PCI based reflective memory real-time fiber optic network product for GE Fanuc embedded systems, belonging to the VMIxxx-5565 series. It can be integrated into the network with other members of the series through standard fiber optic cables, and each board is called a node, allowing computers and other devices with different architectures and operating systems to share data in real time.

Key Features

A high-speed and easy-to-use fiber optic network with a serial rate of 2.12 Gbaud.

Supports PCI 64 bit 66MHz transmission, network operation does not require the involvement of a host processor.

Equipped with redundant operation mode, supporting up to 256 nodes.

The multi-mode fiber optic connection distance can reach up to 300 meters, and the packet size is dynamically variable (4-64 bytes).

The transmission rate varies depending on the packet size, with 47.1MB/s for 4-byte packets and 174MB/s for 64 byte packets.

Equipped with 64MB or 128MB SDRAM reflective memory with parity check, as well as two independent direct memory (DMA) channels, configurable byte order conversion to accommodate multiple CPU architectures on the same network.

Operating principle

Basic operation: Each node in the network is interconnected in a daisy chain loop through fiber optic cables, and each node needs to have a unique node ID (set through 8 onboard jumpers). The data transmission is initiated by the PCI host system writing data to the onboard SDRAM. During the writing process, the onboard circuit automatically writes the data and related information into the transmit FIFO, forming variable length data packets that are transmitted through the fiber optic interface. The receiver opens the data packet and stores it in the receive FIFO, then writes it into the local SDRAM and routes it to its own transmit FIFO until the data returns to the source node and is removed.

Register group: including PCI configuration registers, local configuration registers, runtime registers, DMA control registers, reflective memory (RFM) control and status registers. The functions and purposes of each register group are different, and some registers have different initialization methods and modification frequencies.

Reflective memory RAM: There are two specifications, 64MB or 128MB, with parity check. The starting position is specified by the base address register 3. The parity check function needs to be enabled by setting a specific register, and write operations need to be performed at the 32-bit or 64 bit boundary.

Interrupt circuit: There is a single PCI interrupt output (INTA #), and the interrupt source can be enabled and monitored separately through multiple registers. The interrupt circuit is divided into two layers, and the second layer interrupt is transmitted to the first layer through the LINTi # signal.

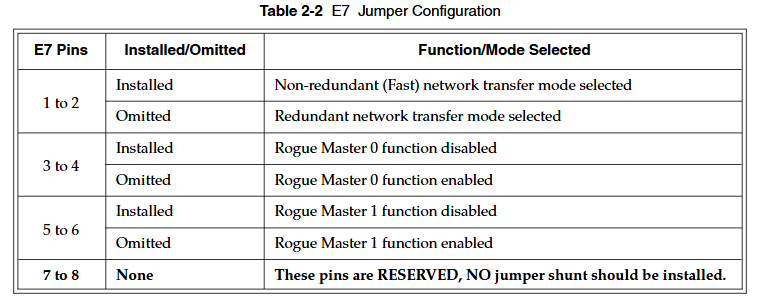

Redundant transmission mode: Removing the jumper blades between pins 1-2 of jumper E7 can configure it as redundant mode. At this time, each data packet is transmitted twice, and the receiving circuit evaluates the transmission situation. Although this mode reduces the probability of data loss, it will also lower the effective network transmission rate.

**Rogue packet removal operation * *: Rogue packets are packets that do not belong to any node in the network. VMIPCI-5565 can run as one of the two Rogue hosts to detect and remove rogue packets. After detection, relevant flags will be set and PCI interrupts can be triggered.

Configuration and Installation

Unpacking procedure: Components are sensitive to static electricity and should be handled on conductive materials. When not in use, they should be stored in their original packaging. Upon receipt, they should be inspected for any transportation damage and claims should be promptly processed.

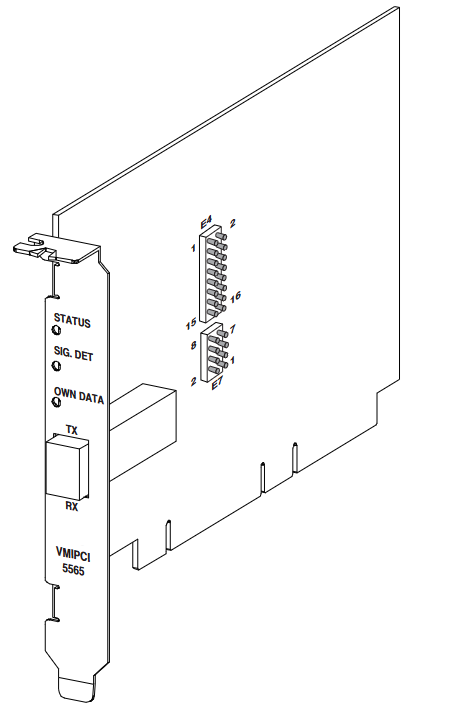

Jumper configuration and position

The node ID is set by the 8 jumper blades of jumper block E4, and each node ID needs to be unique. Install the jumper blade so that the corresponding bit is low (0), and remove it so that it is high (1).

Jumper E7 controls three functions: 1-2 pins select non redundant or redundant network transmission mode, 3-4 pins enable or disable rogue host 0 function, 5-6 pins enable or disable rogue host 1 function, 7-8 pins are reserved pins and should not be installed with jumper blades. The default configuration is to install jumper blades on all pins except 7-8.

Physical installation: Before installation, it is necessary to ensure that the node ID and operation mode have been set. Power off the installation, firmly insert the board into the PCI connector and fix the screws, then reinstall the chassis cover and turn on the power. The board design complies with the PCI 2.2 specification.

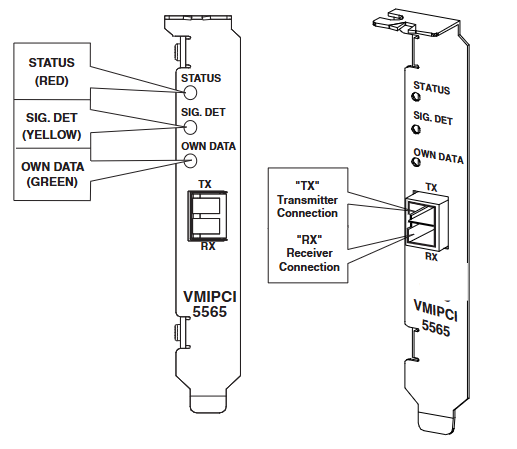

Front panel description: There are three LED indicator lights, the red status LED is user-defined, and it is on by default when turned on. The status can be switched by writing to bit 31 of the control and status registers; The yellow signal detection LED lights up when the receiver detects light; The green self data LED lights up when it detects the return of its own data. There are also "RX" receiver ports and "TX" transmitter ports, which use "LC" type fiber optic cables. Dust caps should be installed when not connected to the cables, and eye injuries should be avoided when not powered.

Cable configuration: Provides cable specifications and connector specifications for multimode or single-mode fiber optic interfaces, including core diameter, cladding diameter, sheath outer diameter, attenuation, bandwidth, and other parameters, as well as connector compatibility, insertion loss, and other information.

Connectivity: Nodes are connected in a circular manner, as in the example of a circular connection of six nodes.

Programming

PCI configuration register: located in the 256 bytes of the PCI configuration space, the first 64 bytes are predefined headers that contain information such as vendor ID and device ID. Some registers can be modified by the user, while others are read-only or initialized by the system BIOS.

Local configuration registers: can be accessed through base address register offset 0 or 1, initialized to normal working configuration by serial EEPROM, and some registers can be modified by users to match the host system.

Runtime register: It is also accessed through the base address register offset 0 or 1, and will not be initialized by the serial EEPROM, maintaining the default state when the PCI bus is reset. Users need to modify some bits to activate the desired operating mode.

DMA control register: accessed through offset 0 or 1 of the base address register, it defaults to the PCI reset state and needs to be modified by the user to activate the operating mode, including DMA channel mode register, address register, etc., used to operate two DMA engines.

RFM control and status register: located in PLX local address space 0, the base address is specified by "PCI base address 2" in the PCI configuration register, including board revision register, node ID register, etc., to achieve the unique function of reflecting the memory board.

DMA operation example: It is necessary to find the value of the base address register 0, set five DMA registers, and then start the transfer and monitor the completion status by writing to the command/status register.

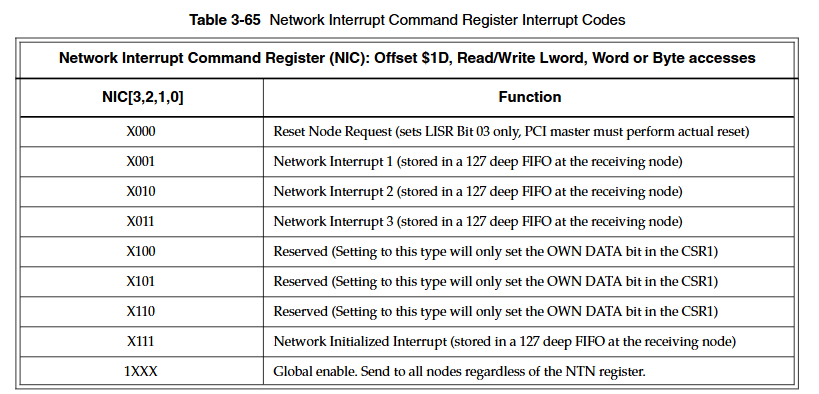

Example of network interrupt handling: including setting steps (clearing previous interrupts in FIFO, setting relevant registers to enable interrupts, etc.) and steps for serving network interrupts (reading registers to determine interrupt source, processing data and sender ID, etc.).

Maintain and comply with information

Maintenance: When the product malfunctions, it is necessary to first check the software, system configuration, electrical connections, etc. If a return is required, please contact GE Fanuc Embedded Systems to obtain a Return Merchandise Authorization (RMA) number. User level repairs are not recommended, and the drawings and charts in the manual are for reference only.

Compliance information: Complies with multiple international standards and regulations, such as the EU's EN series standards, the US FCC Part 15, and Australia/New Zealand's AS/NZS CISPR 22. Compliance requirements and restrictions vary in different regions.

- YOKOGAWA

- Reliance

- ADVANCED

- SEW

- ProSoft

- WATLOW

- Kongsberg

- FANUC

- VSD

- DCS

- PLC

- man-machine

- Covid-19

- Energy and Gender

- Energy Access

- Renewable Integration

- Energy Subsidies

- Energy and Water

- Net zero emission

- Energy Security

- Critical Minerals

- A-B

- petroleum

- Mine scale

- Sewage treatment

- cement

- architecture

- Industrial information

- New energy

- Automobile market

- electricity

- Construction site

- HIMA

- ABB

- Rockwell

- Schneider Modicon

- Siemens

- xYCOM

- Yaskawa

- Woodward

- BOSCH Rexroth

- MOOG

- General Electric

- American NI

- Rolls-Royce

- CTI

- Honeywell

- EMERSON

- MAN

- GE

- TRICONEX

- Control Wave

- ALSTOM

- AMAT

- STUDER

- KONGSBERG

- MOTOROLA

- DANAHER MOTION

- Bentley

- Galil

- EATON

- MOLEX

- Triconex

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- KOLLMORGEN

- Beijer

- Endress+Hauser

- schneider

- Foxboro

- KB

- REXROTH

- YAMAHA

- Johnson

- Westinghouse

- WAGO

- TOSHIBA

- TEKTRONIX

- BENDER

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- XP POWER

- Baldor

- Meggitt

- SHINKAWA

- Other Brands

- other brands

- UniOP

- KUKA

- IBA

-

Hirschmann RS20-0800T1T1SDAEHC09.1.00 Industrial Ethernet Switch Managed Network Switch for Factory Automation and Industrial Communication Systems

-

Omron C500-NC103-E PLC Position Control Module Industrial Automation System for High Precision Machine Control and Factory Integration

-

Omron R88D-HT10 PLC Servo Drive Industrial Motion Control Unit for High Precision Automation Systems and Industrial Machinery Applications

-

Omron R88D-HS22 R88D-H310G R88M-H1K130 Servo Drive System High Precision Motion Control Package for Industrial Automation Applications with Cable

-

Schneider ATV212HD22N4S Variable Speed Drive Industrial Inverter for HVAC Motor Control Energy Efficient Automation System Solution

-

TOYO KEIKI EH-R YH-212 P:CARD5 Industrial Control Card Precision Measurement and Signal Processing Module for Automation Systems

-

Mitsubishi AJ71QLP21G PLC Module Industrial Communication and Control Unit for Factory Automation and System Integration Solutions

-

Mitsubishi A1SX81 Digital Input Module PLC Local Unit for Industrial Automation Signal Acquisition and High Reliability Control Systems

-

Omron F350-L100E Image Processing Unit Industrial Vision System for Automated Inspection and Quality Control Applications

-

Omron NS12-TS01B-V2 HMI Touch Screen Operator Panel Industrial Automation Interface for Machine Control and Visualization Systems

-

Siemens 6SE7090-0XX84-0AG1 CU3 Closed Loop Control Module Industrial Drive and Automation Control System Component

-

ABB P-HC-BRC-40000000 Harmony Bridge Controller Industrial Automation Communication and Integration Module

-

Siemens 6SE7038-6EK84-1JC2 IGD8 Gate Driver Module for Industrial Drive Systems and High Power Inverter Control Solutions

-

Omron B7AM-8B16 PLC Digital I/O Module Expansion Unit for Industrial Automation Control Systems and Signal Processing

-

Omron R7M-A10030-BS1 SmartStep Servo Motor 100W 200V Industrial Motion Control System with Brake Function for Precision Automation

-

B&R 4PP035.0300-01 Operation Panel Industrial HMI Interface for Machine Control, Process Monitoring and Automation Visualization Systems

-

B&R 3AM050.6 PLC Module for Industrial Automation Control System Processing and Machine Control Unit

-

ABB G3ENa HENF450268R2 Industrial Automation Control Module High Performance Processing and Distributed System Interface Unit

-

ABB P5EAa HENF206350R2 Industrial Automation Control Module Advanced Processing and High Reliability System Interface Unit

-

ABB O3EC HENF442581R1 Industrial Automation Control Module High Precision Signal Processing and Distributed System Interface Unit

-

ABB O3EHa HENF315087R2 Industrial Automation Control Module Advanced Signal Processing and System Interface Unit

-

ABB E3ED Industrial Automation Control Module High Stability Signal Processing and Distributed System Interface Unit

-

ABB O3ED Industrial Automation Control Module Signal Processing and Distributed System Interface Unit

-

ABB E3EP HENF315276R1 Industrial Automation Control Module High Precision Signal Processing and System Interface Unit

-

ABB O3EGb HENF315118R2 Industrial Automation Control Module Advanced Signal Processing and System Interface Unit

-

ABB O3ES HENF445789R1 Industrial Automation Control Module Advanced Signal Processing and Distributed System Interface Unit

-

ABB E3EB HENF315129R1 Industrial Automation Control Module High Stability Signal Processing Unit

-

ABB G3ESa HENF318736R1 Industrial Control Module Advanced Automation System Interface Processing Unit

-

ABB 8025-235 Industrial Control and Measurement Module Automation Signal Processing Unit

-

ABB REG216 Industrial Generator Protection and Control System Advanced Power Automation Relay Unit

-

ABB PU512V2 3BUR001401R1 Industrial Processor Unit High Performance Automation Control Module

-

ABB LDMUI-001 61320946C Industrial Drive Control Interface Module High Performance Automation Communication Unit

-

ABB 216NG61A HESG441633R1 HESG216875/K Industrial Control Module Advanced Automation Processing Unit System Interface

-

ABB PFTL201C 50KN 3BSE007913R50 High Precision Load Cell Industrial Tension Measurement and Force Control Sensor Unit

-

ABB RED670 High Performance Line Differential Protection Relay Industrial Power System Protection Unit

-

ABB PP825A 3BSE042240R3 Industrial Panel Controller Advanced Automation HMI Processing Unit

-

ABB SCYC51020 58052582/G Industrial Control and Communication Module High Stability System Interface Unit

-

ABB AO2000 LS25 Industrial Gas Analyzer System High Precision Emission Monitoring and Process Control Unit

-

ABB LM80 Industrial Measurement and Signal Processing Module Automation System Data Acquisition Unit

-

ABB PFEA113-20 3BSE028144R0020 Industrial Tension Control Module High Precision Measurement Unit

-

ABB PM803F 3BDH000530R1 Industrial Controller CPU Automation System Processing Unit

-

ABB SD822 3BSC610038R1 Power Supply Module Industrial Automation System Stable Energy Unit

-

ABB PCD235B1101 3BHE032025R1101 Industrial Control Module High Performance Automation Processing Unit

-

ABB AZ20/112112221112E/STD Industrial Gas Analyzer Control and Monitoring System High Precision Measurement Unit

-

ABB KP3000 Advanced Industrial HMI Panel Operator Control Interface System Unit

-

ABB KP2500 Industrial HMI Operator Panel Human Machine Interface Control Display Unit

-

ABB UFD203A101 3BHE019361R0101 Industrial Interface Control Module Automation Communication Unit

-

ABB GVC736CE101 3BHE039203R0101 Industrial Drive Control Processing Unit High Performance Automation Controller

-

ABB UAD142A01 3BHE012551R0001 Industrial Control and Automation Interface Module High Stability Processing Unit

-

GE HE693STP110 Stepper Motor Control Module for Industrial PLC Systems

-

GE HE693STP104AX Stepper Control Module for PLC Automation System

-

GE DS200TCQAG1BHF Turbine Control Module

-

GE DS200ADGIH1AAA Analog Input Control Board

-

ABB CAI04 Analog Input Module for Industrial Automation System Signal Acquisition and Process Control Interface Unit Replacement

-

ABB FET3251C0P184C0H2 Industrial Control Interface Module for Automation System Signal Processing and Power Management Unit Replacement

-

ABB 5SHY35L4503 IGCT Power Module for Industrial Drive System Inverter Control and High Power Conversion Unit Replacement

-

ABB PM866-2 3BSE050201R1 AC 800M Controller CPU Module for Industrial Automation System Control Processing and Distributed Control System Core Unit

-

ABB CP405 A0 1SAP500405R0001 HMI Touch Panel for Industrial Automation Operator Interface Display Control and Monitoring System

-

ABB R474A11XE HAFAABAAABE1BCA1XE Power Supply Module for Industrial Automation System Control Cabinet Energy Distribution and Interface Support Unit

-

GUTOR OP6257 Industrial Power Control Module | Reliable UPS System Component

-

ABB REF542PLUS 1VCR007346 Protection Relay for Substation Automation Power Distribution Control and Electrical Fault Protection System

-

ABB REF542PLUS 1VCF752000 Protection Relay for Substation Automation Power System Control and Electrical Fault Detection Unit

-

ABB PPD113B03-26-100100 3BHE023584R2625 Drive Control Board for Industrial Automation Excitation System and Power Electronics Control Module

-

ABB PCD232A 3BHE022293R0101 Industrial Drive Control Processing Module Power Electronics Interface Unit

-

ABB PFEA113-65 3BSE050092R65 Tension Control Module Industrial Automation Measurement Unit

-

ABB XVC767AE102 3BHB007209R0102 Industrial Drive Control Board Power Electronics System Module

-

ABB CI857K01 3BSE018144R1 Communication Interface Module for Industrial Automation System Control Network Integration and Data Exchange Gateway Unit

-

ABB 3ASC25H219B DATX133 Advanced Signal Interface Module for Industrial Automation System Multi-Channel Communication and Control Data Optimization Unit

-

ABB 3ASC25H214 DATX130 High-Speed Signal Interface Module for Industrial Automation System Communication Upgrade and Control Data Processing Unit

-

ABB 3ASC25H208 DATX100 Signal Interface Module for Industrial Automation System Communication Processing and Control Data Exchange Unit

-

ABB 3ASC25H204 DAPU100 Data Processing Unit for Industrial Automation System Control Coordination and High-Speed System Data Management Module

-

ABB 3ASC25H216A DATX132 Signal Interface Module for Industrial Automation System Control Expansion and High-Speed Data Communication Unit

-

ABB LWN2660-6 Power Supply and Network Interface Module for Industrial Automation System Control Cabinet Energy Distribution and Communication Support Unit

-

ABB ICSE08B5 FPR3346501R1012 Control and Signal Processing Module for Industrial Automation System Interface and System Expansion Unit

-

ABB 1MRK00008-KB Protection and Measurement Module for Power System Relay Control Industrial Substation Automation Unit

-

ABB UAD155A0111 3BHE029110R0111 Interface Module for Industrial Automation System Communication Control and Signal Processing Unit

-

ABB PM511V08 3BSE011180R1 Processor Unit for ABB Industrial Automation Control System CPU Module High Performance PLC and DCS Controller Unit

-

ABB PU515A 3BSE032401R1 Processor Unit for ABB Industrial Automation System Control Processing and High Performance PLC System Core Module

-

ABB TU810V1 3BSE013230R1 Terminal Unit for ABB S800 I/O System Industrial Automation Module Connection and Signal Interface Base Unit

-

ABB XO08R2 1SBP260109R1001 Digital Output Module for ABB PLC System Industrial Automation I/O Control Expansion Unit

-

ABB 3BHL000986P0006 Drive Control Power Module for Industrial Converter System High Power Automation and Motor Drive Control Unit

-

ABB SC540 3BSE006096R1 Control System Module for Industrial Automation PLC DCS Control and System Communication Processing Unit

-

ABB 5SHY4045L0001 IGBT Power Module 3BHB018162R0001 3BHE009681R0101 GVC750BE101 for High Power Industrial Drive and Converter Systems

-

ABB P4LQA HENF209736R0003 Control Interface Module for Industrial Automation System Signal Processing and System Integration Unit

-

ABB FENA-11 Ethernet Adapter Module for ABB Drives Industrial Communication Interface and Network Control Unit

-

ABB COM0003 2RAA005844A0006A Communication Processor Module for Industrial Automation System Network Control and Data Exchange Unit

-

ABB AIM0006 2RCA021397A0001F Communication Interface Module for Industrial Automation System Integration and Data Exchange Unit

-

ABB S-073N 3BHB009884R0021 Drive Control Module for ABB High Power Converter and Industrial Drive System Power Interface Unit

-

ABB REF615E Feeder Protection Relay HBFHAEAGNCA1BNN1XE Intelligent Protection Device for Power Distribution and Electrical Automation Systems

-

Meggitt C327845-11 Industrial Control Module | High Reliability Automation Component

-

ABB TP830 3BSE018114R1 Industrial Operator Panel HMI Interface Unit Automation Control Display Module

-

ABB DSAI146 3BSE007949R1 Industrial Analog Input Module Automation System Signal Interface Unit

-

ABB 5SHX2645L0004 3BHL000389P0104 IGBT Power Module for High-Power Industrial Drive System and ABB Converter Control Unit

-

ABB LC-608 Industrial Logic Control Module for ABB Automation System Interface Signal Processing and Control Integration Unit

-

ABB TK803V018 3BSC950130R1 System Interface Module for ABB DCS Automation Network Configuration and Industrial Control Support Unit

-

ABB RF522 3BSE000743R1 Communication Interface Module for ABB DCS System Network Node and Industrial Automation Control Integration Unit

-

ABB DSRF197 3BSE019297R1 Communication Interface Module for ABB DCS Industrial Automation System Signal and Network Control Unit

-

ABB DSBC176 3BSE019216R1 Bus Extender Board Industrial Communication Module for ABB DCS and PLC System Network Expansion Unit

-

ABB DSAO120A 3BSE018293R1 Analog Output Module Industrial Control I/O Unit for ABB DCS Automation System Process Control

-

ABB DSDP170 57160001-ADF Distributed I/O Processing Module for ABB DCS Automation System Expansion and Control Integratio

-

ABB DSDO115A 3BSE018298R1 Digital Output Module Industrial Control I/O Unit for ABB DCS Automation System

-

ABB DSDI110AV1 3BSE018295R1 Digital Input Module Industrial I/O Unit for ABB DCS Automation System Signal Acquisition

-

ABB 5SHY3545L0010 3BHB013088R0001 GVC750BE101 High Power IGBT Module for ABB Industrial Drive and Inverter System

-

ABB 81943A041-1 Industrial System Expansion Interface Module for ABB Automation and Control System Integration Unit

-

ABB SA168 3BSE003389R1 Signal Processing Module Industrial Analog Input Interface Unit for ABB Automation System

-

ABB PM865K01 3BSE031151R1 AC 800M Controller PLC Central Processing Unit Industrial Automation Control Module

-

ABB 5SHY3545L0016 3BHB020720R0002 GVC736BE101 IGBT Power Module High Power Inverter Module for ABB Drive System

-

ABB TP853 3BSE018126R1 HMI Operator Panel Industrial Control Touch Display Unit for ABB Automation System

-

ABB REM545AG228AAAA Advanced Protection Relay Industrial Power System Automation Control Device

-

ABB CI626A 3BSE005029R1 Industrial Communication Interface Module Distributed Control System Unit

-

ABB NDCU-12C Industrial Drive Control Unit Automation System Communication Module

-

ABB REM615C_D HCMJAEADAND2BNN1CD Protection and Control Relay Industrial Power System Automation Device

-

ABB IBA 940143201 Industrial Bus Adapter Module Automation Communication Interface Unit

-

ABB PFSK151 3BSE018876R1 Industrial Signal Processing Control Module Automation System Unit

-

ABB IDPG 940128102 Industrial Digital Power Control Module Automation System Component

-

ABB OCAH 940181103 Industrial System Interface Module for ABB DCS Communication and Signal Adaptation Unit

-

ABB OCAHG 492838402 Industrial Communication Interface Module for ABB DCS Control System Integration Unit

-

ABB PPD539 A102 3BHE039770R0102 Process Control Unit Industrial Automation Controller Module for ABB System

-

ABB PP825 3BSE042240R1 Basic HMI Operator Panel Industrial Control Display Unit for ABB Automation System

-

ABB TP857 3BSE030192R1 HMI Touch Panel Industrial Operator Interface Display Unit for ABB Automation System

-

ABB PP865A 3BSE042236R2 HMI Operator Panel Industrial Human Machine Interface Display Unit for ABB Control System

-

ABB SCYC51020 58052582H Drive Control Interface Board Industrial Inverter Communication Module

-

ABB SCYC51010 58052515G Drive Control Interface Board Industrial Inverter Signal Interface Unit

-

ABB CB801 3BSE042245R1 Control Board Industrial Drive System Central Control Unit for ABB IGBT Inverter System

-

ABB SCYC51090 58053899E IGBT Protection Control Board Industrial Drive Protection Unit for ABB Inverter System

-

ABB SCYC51040 58052680E Gate Driver Control Board Industrial IGBT Drive Control Unit for ABB Power System

-

ABB 5SHY4045L0001 3BHB018162R0001 High Power IGBT Module Industrial Drive Inverter Power Semiconductor Device

-

ABB 5SHY6545L0001 AC10272001R0101 5SXE10-0181 High Power Semiconductor Module Industrial Drive Control Component

KONG JIANG

Add: Jimei North Road, Jimei District, Xiamen, Fujian, China

Tell:+86-15305925923