K-WANG

XYCOM XVME-100 memory module

XYCOM XVME-100 memory module

Product Overview and Core Positioning

Product definition: XYCOM XVME-100 is a single height (3U) VMEbus compatible memory expansion module for industrial control systems, designed to provide RAM, EPROM, mask ROM, or EEPROM storage expansion for VMEbus architecture systems, supporting flexible configuration and data backup.

Core values:

High compatibility: fully compliant with the VMEbus C1 standard, seamlessly integrated into the VMEbus system;

Flexible expansion: Dual storage group design, supporting multiple capacities and types of storage chips, adapting to different scene requirements;

Data security: onboard battery backup and undervoltage protection circuit to prevent data loss caused by power failure;

Independent configuration: Independent settings of storage group address, chip speed, backup power, and other parameters are achieved through jumper wires.

Applicable scenarios: VMEbus architecture devices that require reliable memory expansion, such as industrial automation control, military electronic equipment, embedded systems, etc.

Key specification parameters

(1) Core Performance Parameter Table

Specific specifications of the project

Storage capacity RAM/EPROM/Mask ROM: Maximum 1MB; EEPROM: Maximum 256KB

Design 2 storage groups (Bank1/Bank2), each with 4 32 pin JEDEC slots, supporting independent configuration

Compatible chip specifications and capacities: 8K × 8, 16K × 8, 32K × 8, 64K × 8, 128K × 8 (EEPROM limited to 32K × 8 and below);

Speed: 100ns, 150ns, 200ns, 250ns

Power requirements: Working power supply:+5V DC (typical 900mA, maximum 1A);

Backup power supply: onboard battery (1.4Ah, typical lifespan of 6 years) or+5V STDBY

Bus compatible with VMEbus C1 standard, A24 address space, DTB slave device

Physical specification 3U Form Factor (single height), size meets VMEbus standard

(2) Environmental and Reliability Parameter Table

Specific specifications of environmental category

Working temperature: 0 ° C~65 ° C (32 ° F~149 ° F)

Storage temperature -40 ° C~85 ° C (-40 ° F~158 ° F)

Humidity 5%~95% RH, non condensing (anti-static protection is required for extremely low humidity)

Altitude work: 0~3048m (10000ft); Storage: 0~15240m (50000ft)

Vibration (working) 5~2000Hz, peak acceleration 10g, peak to peak displacement 0.025mm (maximum)

Impact (working) 30g peak acceleration, 11ms duration

Core functions and design highlights

(1) Storage and configuration functions

Dual storage group independent configuration: Bank1 and Bank2 can set VME address, chip size, address modifier decoding, chip speed, and backup power type separately through jumper wires, supporting mixed use of chips of different specifications;

Multi type storage support: compatible with RAM, EPROM, mask ROM, EEPROM four storage types, EEPROM needs to support fast write/polling technology and TTL logic level;

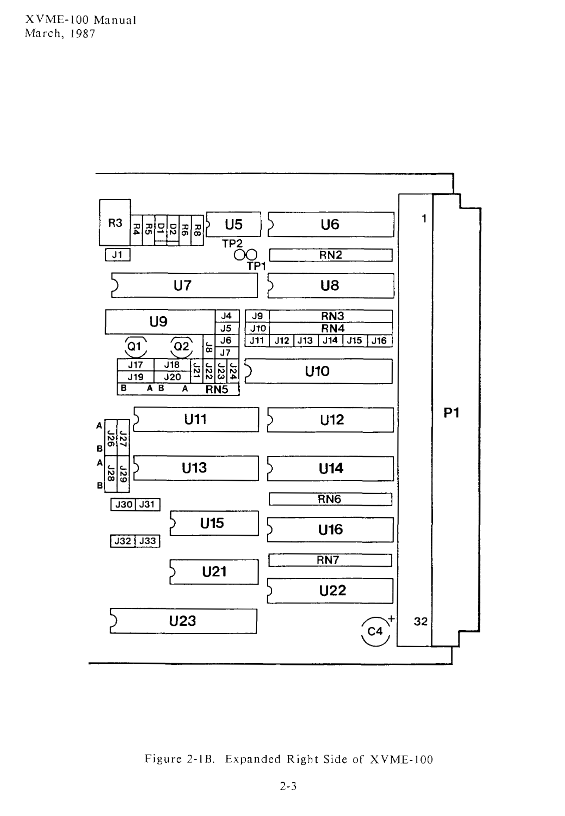

Flexible allocation of address space: Set the base address through J14-J24 (Bank1) and J16/J26-J33 (Bank2) jumpers, and the address space occupied by the storage group is 4 times the chip capacity, which needs to be aligned to the 4 times capacity boundary.

(2) Data protection mechanism

Undervoltage protection: Equipped with a built-in power monitor, the storage chip is automatically disabled when the+5V voltage is lower than 4.75V to prevent data writing errors. The SYSRESET * drive signal can be optionally enabled;

Dual options for backup power: supports onboard battery backup (compatible with low-power RAM chips) or VMEbus+5V STDBY backup, switched via J34/J35 jumper;

Data anti write design: automatically cuts off the write path of the storage chip in case of power failure, combined with battery backup to ensure long-term storage of RAM data.

(3) Bus and interface characteristics

VMEbus signal compatibility: supports IACKIN */ACKOUT * daisy chain and BUS GRANT signal direct connection, complying with the address, data, and control signal definitions of VMEbus C1 standard;

P1 connector interface: 3-row pin design, including address bus (A01-A23), data bus (D00-D15), control signals (AS *, DS0 */DS1 *, DTACK *, etc.), and power pins;

Status indication: Each storage group is equipped with a green LED that lights up instantly when accessed, providing visual feedback on the working status.

Installation and configuration process

(1) Key items for jumper configuration

Configure Category Jumper Position Core Function

Address/chip size Bank1: J14/J17-J24/J50-J52;

Bank2: J16/J26-J33/J47-J49 Set VME base address (A15-A23) and chip capacity (8K × 8~128K × 8)

Address modifier decoding Bank1: J10-J13;

Bank2: J9/J12/J15 Configure privileged access (super user only/all users), data/program space access permissions

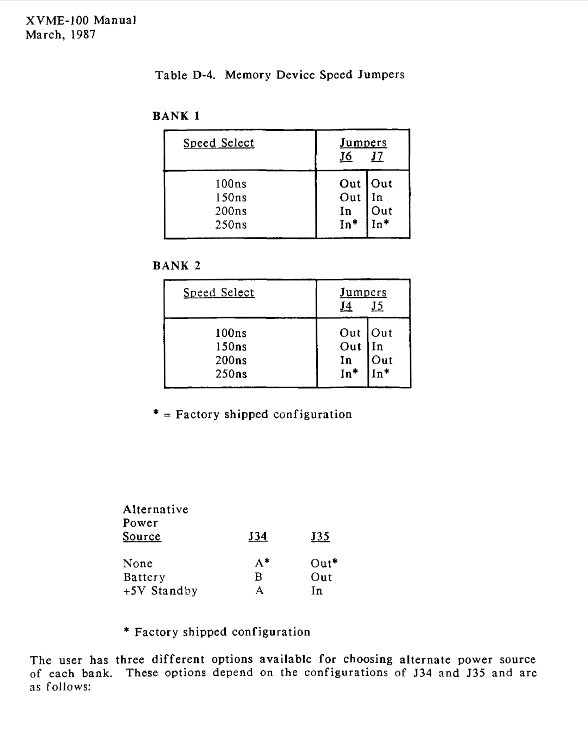

Chip speed selection Bank1: J6-J7;

Bank 2: J4-J5 matching storage chip speed (100ns/150ns/200ns/250ns)

Definition of memory chip pins Bank1: J40-J46;

Bank2: Pin definitions for adapting J2/J3/J25/J36-J39 to different types of storage chips (such as EPROM/RAM pin differences)

Select J34-J35 for backup power and switch between battery backup/+5V STDBY backup/no backup mode

(2) Installation steps

Chip installation: In the power-off state, configure the corresponding jumper according to the storage type, align the storage chip with the slot gap direction, evenly insert it into the 32 pin slot with force, and ensure that the pins are fully in contact;

Rack deployment: Align the module with the VMEbus rack rail, slowly push it in until the connector is fully engaged, and secure the front panel with screws. Each module occupies one 3U slot;

Optional 6U panel installation: If you need to adapt to a 6U rack, you can replace the XVME-945 6U front panel kit and transfer the handle and identification plate according to the manual steps;

Calibrate power monitor: It has been calibrated at the factory. If recalibration is required, adjust the POT R3 potentiometer with a 4.75V reference power supply to ensure accurate triggering threshold for undervoltage protection.

Safety and usage precautions

Battery safety: Short circuit, charging, reverse connection, welding or heating of batteries are prohibited. Waste should be treated as industrial waste to avoid high temperature and contact with metal surfaces;

Static electricity protection: When operating modules and storage chips, it is necessary to release human static electricity, especially CMOS RAM chips are sensitive to static electricity;

Installation taboos: It is forbidden to plug and unplug modules with power on. When inserting, avoid applying too much force to bend the pins and ensure that the module is aligned with the rack rails;

Special requirements for EEPROM: EEPROM must support fast write/polling technology and must use TTL logic level, otherwise it may cause abnormal operation.

- YOKOGAWA

- Reliance

- ADVANCED

- SEW

- ProSoft

- WATLOW

- Kongsberg

- FANUC

- VSD

- DCS

- PLC

- man-machine

- Covid-19

- Energy and Gender

- Energy Access

- Renewable Integration

- Energy Subsidies

- Energy and Water

- Net zero emission

- Energy Security

- Critical Minerals

- A-B

- petroleum

- Mine scale

- Sewage treatment

- cement

- architecture

- Industrial information

- New energy

- Automobile market

- electricity

- Construction site

- HIMA

- ABB

- Rockwell

- Schneider Modicon

- Siemens

- xYCOM

- Yaskawa

- Woodward

- BOSCH Rexroth

- MOOG

- General Electric

- American NI

- Rolls-Royce

- CTI

- Honeywell

- EMERSON

- MAN

- GE

- TRICONEX

- Control Wave

- ALSTOM

- AMAT

- STUDER

- KONGSBERG

- MOTOROLA

- DANAHER MOTION

- Bentley

- Galil

- EATON

- MOLEX

- Triconex

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- KOLLMORGEN

- Beijer

- Endress+Hauser

- schneider

- Foxboro

- KB

- REXROTH

- YAMAHA

- Johnson

- Westinghouse

- WAGO

- TOSHIBA

- TEKTRONIX

- BENDER

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- XP POWER

- Baldor

- Meggitt

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- IBA

-

ABB PFSA240 Roll DC Supply Unit 3BSE073476R1 Industrial Stressometer Power Supply Module for Rolling Mill Systems

-

ABB PFSA107-Z42 DTU Stressometer Digital Transmission Unit High Precision Strip Tension Measurement Module

-

GE AT868-2-1-1 Ultrasonic Flow Transmitter AquaTrans AT868 Dual Channel Industrial Flow Meter

-

ABB SCC-C 23070-0-10232110 Industrial Control Module Automation System Communication Controller

-

APPLIED MATERIALS 0041-96185 - Heater Assy with 0150-45776 0190-60492 AMAT

-

APPLIED MATERIALS 0021-33426 - SHIELD INNER SINGLE 300MM NO COIL AMAT

-

APPLIED MATERIALS 0140-01905 - HARNESS ASSY DUAL IHC PRESS CONT ADAPTER 16798 AMAT

-

APPLIED MATERIALS 0051-01848 - LINE VAC EXHAUST CH Y LEAK CHECK PORT EPI AMAT

-

APPLIED MATERIALS 0010-02863 - P5000 150mm Teos Susceptor AMAT

-

APPLIED MATERIALS 0010-14056 - ASSY INJECT NOZZLE STANDARD AMAT

-

APPLIED MATERIALS 0020-34694 - LINER GDP R2 OXIDEGECO AMAT

-

APPLIED MATERIALS 0195-07416 - SYCAMORE-X CMP POLISHER I/O ASSEMBLY AMAT

-

APPLIED MATERIALS 0200-09036 - WAFER LIFT PIN AMAT

-

APPLIED MATERIALS 0021-39090 - FLANGE 10" CONFLAT ADAPTOR AMAT

-

APPLIED MATERIALS 0100-99011 - GAS INTERLOCK AMAT

-

APPLIED MATERIALS 0100-11002 - digital I/O card AMAT

-

APPLIED MATERIALS 0190-40000 - PNEUMATIC MANIFOLD CHAMBER 32903 AMAT

-

APPLIED MATERIALS 0021-39792 - PERF PLATE OX. 200 MM TEOS 21896 AMAT

-

APPLIED MATERIALS 0040-04896 - BELL JAR QUARTZ Q-KOTE 200MM AMAT

-

APPLIED MATERIALS 0020-20653 - BASE HEATER AMAT

-

APPLIED MATERIALS 0190-75057 - Lift Cylinder Assy AMAT

-

APPLIED MATERIALS 0010-70345 - Applied Materials 0042-01927

-

APPLIED MATERIALS 0100-91024 - PWBA PRE-ACCEL VENDOR I/F PCB 9500 IMPLANT AMAT

-

APPLIED MATERIALS 0041-56144 - HEATER PEDESTAL ASSEMBLY ENP FCVD EDGE AMAT

-

APPLIED MATERIALS 0090-00836 - SOURCE MOTOR ASSY 0040-24074 GFB5G10 FBLM5120W AMAT

-

MKS 0190-63631 - MASS FLOW VERIFIER MFVA-33168 AMAT

-

APPLIED MATERIALS 0100-35070 - ASSY PCB RF GENERATOR INTERFACE AMAT

-

APPLIED MATERIALS 0010-32221 - ASSEMBLY ROUGH THROTTLE VALVE DRIVE 300MM AMAT

-

SANYO DENKI 0190-14713 - P30B06040HXS8RM AC SERVO MOTOR BL SUPER AMAT

-

APPLIED MATERIALS 0190-14224 - FLEX DIST PANEL AMAT

-

APPLIED MATERIALS 0190-23897 - SPECIFICATION EXMP SYNCNET STAND ALON 14535 AMAT

-

APPLIED MATERIALS 0010-04542 - HEATER ASSY 200MM FC WXZPLUS OSCR 15607 AMAT

-

APPLIED MATERIALS 0190-51414 - AC SERVO DRIVER SGDV-OCA05AY890AA AMAT

-

APPLIED MATERIALS 0020-31747 - P5000 LOADLOCK LID WAFER TXR CHMBR 0020-32930 12573 AMAT

-

APPLIED MATERIALS 0620-01727 - CABLE ASSY SIGNAL RBN 50PIN DSUB EMI RES 17781 AMAT

-

APPLIED MATERIALS 0190-A9510 - IP POWER SUPPLY 33361 AMAT

-

APPLIED MATERIALS T1101-05-000-30 - CRYO TIGER COMPRESSOR AMAT

-

APPLIED MATERIALS 0040-13338 - LINK 1 UPPER 7.2 DEGREE OFFSET CR 300MM 38177 AMAT

-

APPLIED MATERIALS 0190-06926 - Cable SQS R/A TO SQS R/A #2 AMAT

-

APPLIED MATERIALS 0200-00705 - EDGE RING THIN 200MM AMAT

-

APPLIED MATERIALS 0190-01399 - INLINE O3 SNSR ULTRA FULL FLOW HI-CON 6627 AMAT

-

APPLIED MATERIALS 0190-21054 - RF MATCH CABLE ASSEMBLY PRECLEAN 2 AMAT

-

APPLIED MATERIALS 0041-12156 - REFLECTOR PLATE INJECT 300MM RADIANCE PLUS 29763 AMAT

-

MKS 0100-03680 - PCB CHMBR DIST 0090-09483 AS00363-16 35465 AMAT

-

APPLIED MATERIALS E11355460 - Plasma Detector E11355470 Rev.B AMAT

-

APPLIED MATERIALS 0021-33981 - LOWER SHIELD AMAT

-

APPLIED MATERIALS 0100-00583 - GAS PANEL CONTROLLER DIST AMAT

-

APPLIED MATERIALS 0010-54820 - IPC VALVE ASSEMBLY FM 1/2" INTER-PLATEN SPRAY AMAT

-

APPLIED MATERIALS 0020-31747 - P5000 LOADLOCK LID WAFER TXR CHMBR 0020-32930 12573 AMAT

-

APPLIED MATERIALS 0020-40566 - BLANK-OFF POSITION E-F ENP AMAT

-

APPLIED MATERIALS 0021-31023 - Flange Spacer Automatch Single RPS Producer SE AMAT

-

APPLIED MATERIALS 0020-21225 - WEIGHT RING 300MM TITAN PROFILER AMAT

-

APPLIED MATERIALS 0190-A9510 - IP POWER SUPPLY 33361 AMAT

-

APPLIED MATERIALS 0100-90618 - PCB H1 GROUND PDU MOTHER BOARD 0100-90036 AMAT

-

APPLIED MATERIALS 0010-04542 - HEATER ASSY 200MM FC WXZPLUS OSCR 15607 AMAT

-

APPLIED MATERIALS 0020-31658 - CLAMP VESPEL OX-MLR-NIT 200MM AMAT

-

APPLIED MATERIALS 0021-09974 - WINDOW SAPPHIRE PUMPING PLATE AMAT

-

APPLIED MATERIALS 0051-01849 - LINE VAC EXHAUST ELBOW CH Y FAC TRAY EPI 30 AMAT

-

APPLIED MATERIALS 0010-29842 - 300mm DBR High Temp Belt Wrist Titanium AMAT

-

APPLIED MATERIALS 1410-01166 - Heating Jacket AMAT

-

APPLIED MATERIALS 0620-01727 - CABLE ASSY SIGNAL RBN 50PIN DSUB EMI RES 17781 AMAT

-

APPLIED MATERIALS 0010-70345 - Applied Materials 0042-01927

-

APPLIED MATERIALS 0090-00836 - SOURCE MOTOR ASSY 0040-24074 GFB5G10 FBLM5120W AMAT

-

APPLIED MATERIALS 0190-46837 - INFRARED THERMOMETER COMM BOX RAYMI3COMM 30009 AMAT

-

APPLIED MATERIALS 0020-31886 - FLANGE INSULATION UNIBODY .400 THK AMAT

-

APPLIED MATERIALS 0010-05920 - CONTROLLER CCM PROD ETCH CS-PM CARD CAGE AMAT

-

APPLIED MATERIALS 0242-30292 - KIT 20 SCCM MFC W/HRDWR UNIBODY 6449 AMAT

-

APPLIED MATERIALS 0040-41061 - JIG FOUR PT LEVELING TOOL TXZ 300MM AMAT

-

APPLIED MATERIALS 0020-30287 - ADAPTER RING PUMPING PLATE 200MM COMMO AMAT

-

APPLIED MATERIALS 0041-12156 - REFLECTOR PLATE INJECT 300MM RADIANCE PLUS 29763 AMAT

-

APPLIED MATERIALS 0010-37866W - ASSY INT ISRM MODULE FULL SCAN SMG AMAT

-

APPLIED MATERIALS 0090-08137 - 300MM TXZ DLI HEATER CONTROLLER MODULE AMAT

-

APPLIED MATERIALS 0040-20006 - ARM WELDMENT SOURCE STD 8464 AMAT

-

APPLIED MATERIALS 0090-07392 - Dual RF filter AMAT

-

APPLIED MATERIALS 0190-06926 - Cable SQS R/A TO SQS R/A #2 AMAT

-

APPLIED MATERIALS 0020-70279 - LIFTER 150MM WAFER ORIENTER P5000 AMAT

-

APPLIED MATERIALS 0190-35652 - SERIPLEX MUX I/O PCB AMAT

-

APPLIED MATERIALS 0100-11002 - digital I/O card AMAT

-

APPLIED MATERIALS E11355460 - Plasma Detector E11355470 Rev.B AMAT

-

APPLIED MATERIALS 0010-19188 - ASSY COOLDOWN LIFT 34703 AMAT

-

APPLIED MATERIALS 0100-00975 - PCB STEPPER CONTROLLER 2 8099 AMAT

-

APPLIED MATERIALS 0190-16236 - MOTOR ENCODER ASSY ROBOT WRIST MIRRA CMP AMAT

-

APPLIED MATERIALS 0040-48671 - LEFT GUIDE 300MM L-DOOR 37961 AMAT

-

MKS 0100-03680 - PCB CHMBR DIST 0090-09483 AS00363-16 35465 AMAT

-

APPLIED MATERIALS 0190-01399 - INLINE O3 SNSR ULTRA FULL FLOW HI-CON 6627 AMAT

-

APPLIED MATERIALS 8330 - Pair Of Side viewport Panels AMAT

-

APPLIED MATERIALS 0190-75057 - Lift Cylinder Assy AMAT

-

APPLIED MATERIALS 0100-02016 - PCB ASSY ANALOG SYNC DETECT 904-125N AMAT

-

Abaco Systems 0090-08517 - VMICPCI-7326 PCB 38085 AMAT

-

APPLIED MATERIALS 0100-20069 - ASSY WAFER ORIENTER BOARD 0100-02797 AMAT

-

ELEKTRO-AUTOMATIK EA-PS 9036-070 - S01 POWER SUPPLY 625-795365 AMAT

-

APPLIED MATERIALS 3310-00139 - CAPACITANCE PIRANI GAUGE C-SEAL MOUNT 15-PIN AMAT

-

APPLIED MATERIALS 0010-00510 - ASSY BEARING STD 36806 AMAT

-

APPLIED MATERIALS 0041-13895 - FACEPLATE 26MIL CENTERHOLE RF CAP 300MM SACVD 13964 AMAT

-

APPLIED MATERIALS T1101-05-000-30 - CRYO TIGER COMPRESSOR AMAT

-

APPLIED MATERIALS 0050-10076 - WELDMENT DUAL HE MANF SACVD 20243 AMAT

-

MKS 0190-48179 - AS01294-05237-030 Hardened DeviceNet I/O Block AMAT

-

APPLIED MATERIALS 0240-75102 - 8" Transfer Blade 200mm End Effector AMAT

-

APPLIED MATERIALS 0110-90770 - Index Control PCB AMAT

-

APPLIED MATERIALS 0090-91209 - SOURCE SUPPRESSION CLAMPING BOX AMAT

-

APPLIED MATERIALS 0200-01427 - ISOLATOR CERAMIC CVD LOW K 300MM PROD AMAT

-

APPLIED MATERIALS 0021-03637 - FACEPLATE SILANE PRODUCER 200MM AMAT

-

APPLIED MATERIALS 0010-09837 - Wafer Lift Tungsten Precision 5000 AMAT

-

APPLIED MATERIALS 0101-57014 - PCB DEFLECTION-AMPLIFIER BOARD D-AMP 50-06 26296 AMAT

-

APPLIED MATERIALS 0190-36715 - PCB GP IO DISTRIBUTION AMAT

-

APPLIED MATERIALS 0660-00078 - PCB ASSY DNET ANALOG I/O CDN396 DIP-506-068 13392 AMAT

-

APPLIED MATERIALS 0190-B4670 - FIBER HARNESS DVD2-SBBI AMAT

-

APPLIED MATERIALS 1080-02356 - ACCELNET SINGLE AXIS SERVO DRIVE 800-2122 AMAT

-

APPLIED MATERIALS 0040-02937 - WATER MANIFOLD TXZ CIP 200 & 300MM AMAT

-

APPLIED MATERIALS 0040-08944 - LID ANNEAL ECP 200MM AMAT

-

SMC INOI-7134-111 - 4-PORT DEVICENET UPA MODULE Pressure Control AMAT

-

SMC INOI-7134-21 - 4-PORT DEVICENET UPA MODULE Pressure Control AMAT

-

APPLIED MATERIALS 0100-40024 - ASSY WPCBA LOADLOCK INTERCONNECT BOARD AMAT

-

APPLIED MATERIALS 0660-01635 - Chamber P2 Board A AMAT

-

APPLIED MATERIALS 0041-31945 - DOOR ENP ALUM SPD SLIT VALVE VITON LLK 3 AMAT

-

APPLIED MATERIALS 0040-48671 - LEFT GUIDE 300MM L-DOOR 37961 AMAT

-

APPLIED MATERIALS 0051-01849 - LINE VAC EXHAUST ELBOW CH Y FAC TRAY EPI 30 AMAT

-

APPLIED MATERIALS 0040-81661 - CATHODE FACILITY PLATE 35320 AMAT

-

APPLIED MATERIALS 0040-20006 - ARM WELDMENT SOURCE STD 8464 AMAT

-

APPLIED MATERIALS 0110-90770 - Index Control PCB AMAT

-

APPLIED MATERIALS 8330 - Pair Of Side viewport Panels AMAT

-

APPLIED MATERIALS 0040-81155 - LINER LOWER AMAT

-

APPLIED MATERIALS 0100-90618 - PCB H1 GROUND PDU MOTHER BOARD 0100-90036 AMAT

-

APPLIED MATERIALS 0040-47677 - FACEPLATE SIN XG DXZ DCVD AMAT

-

APPLIED MATERIALS 0020-31658 - CLAMP VESPEL OX-MLR-NIT 200MM AMAT

-

CTI-CRYOGENICS 0190-54040 - ON-BOARD IS CONTROLLER 34633 AMAT

-

APPLIED MATERIALS 0020-21665 - SHIELD AL/TI 8 INCH WAFER AMAT

-

APPLIED MATERIALS 0090-10397 - RF FILTER BOX AMAT

K-JIANG

Add: Jimei North Road, Jimei District, Xiamen, Fujian, China

Tell:+86-15305925923