+086-15305925923

K-WANG

Service expert in industrial control field!

Product

Article

NameDescriptionContent

Adequate Inventory, Timely Service

pursuit of excellence

Ship control system

Equipment control system

Power monitoring system

Current position:

新闻动态

newS

Brand

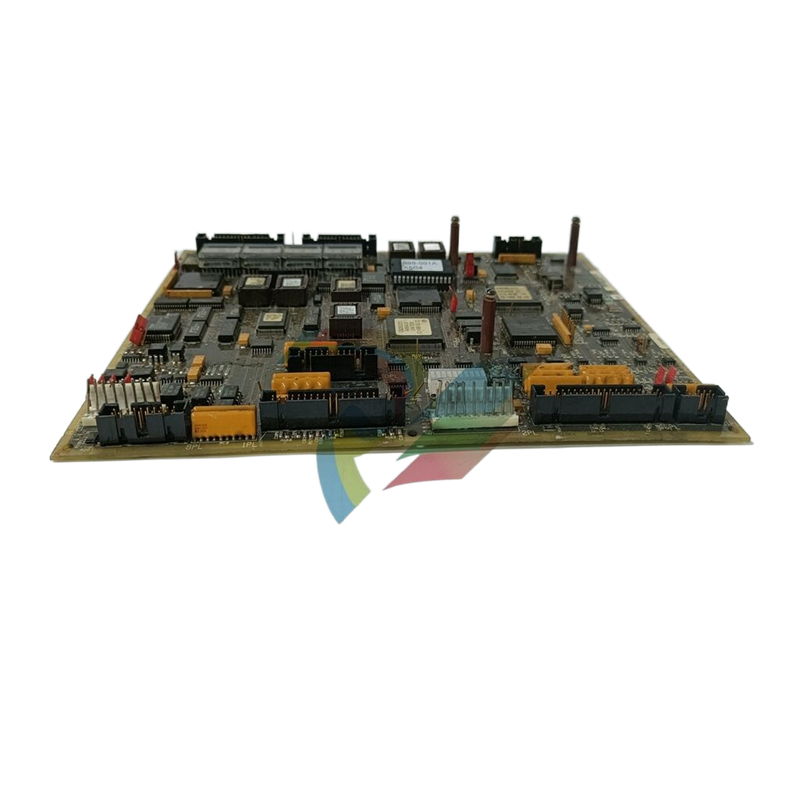

GE IC697MDL740 24/48 VDC Output, 2 Amp, Positive Logic

GE IC697MDL740 24/48 VDC Output, 2 Amp, Positive Logic

GE IC697MDL740 24/48 VDC Output, 2 Amp, Positive Logic

two micro DB-9 connectors located on the front panel. The

micro DB-9 connectors require two micro DB-9 to standard

DB-9 adapters, VMIC P/N 360-010050-001.

PMC EXPANSION SITE — The VMIVME-7700

provides one IEEE 1386.1, 5 V PCI mezzanine card (PMC)

expansion site. This expansion capability allows the

addition of peripherals offered for PMC applications. The

PMC site provides for standard I/O out the VMEbus front

panel. An optional I/O connection to the VMEbus P2

connection can be provided.

KEYBOARD and MOUSE PORTS — The

VMIVME-7700 supports a PS/2 keyboard and mouse

through the front panel.

HARDWARE RESET — A hardware reset switch is

accessible from the front panel.

PROGRAMMABLE TIMER — The VMIVME-7700

provides the user with two 16-bit timers and two 32-bit

timers. These timers are mapped in PCI memory space, are

completely software programmable and can generate PCI

bus interrupts.

WATCHDOG TIMER — The VMIVME-7700

provides a software-programmable Watchdog timer. The

Watchdog timer is enabled under software control. Once the

timer is enabled, software must access the timer within the

specified time period, or the output of the Watchdog timer

will reset the unit.

NONVOLATILE SRAM — The VMIVME-7700

provides 32 KB of nonvolatile SRAM. The contents of the

SRAM are preserved when +5 V power is interrupted or

removed from the unit.

CMOS BATTERY — The VMIVME-7700 uses a

holder that permits field replacement of the CMOS battery.

A header and jumper allows the battery to be disconnected

from the circuitry for long-term storage.

ANNUNCIATORS — Indicators for the board status,

+5 V power good, are provided on the front panel. In

addition, two indicators for the Ethernet adapter activity are

located on each RJ45 network connector.

THERMAL MANAGEMENT — The VMIVME-7700

utilizes a passive heat sink that relies on forced air cooling

within the equipment rack at the specified flow rate. Please

refer to the environmental specifications for more

information.

VMEbus INTERFACE — The VMIVME-7700

VMEbus interface is based on the Universe IID high

performance PCI-to-VMEbus interface from

Newbridge/Tundra.

SYSTEM CONTROLLER — The VMEbus system

controller capabilities allow the board to operate as a slot 1

controller, or it can be disabled when another board is acting

as the system controller. The system controller may be

programmed to provide the following modes of arbitration

Round Robin (RRS)

Single Level (SGL)

Priority (PRI)

The system controller provides a SYSCLK driver,

IACK* daisy-chain driver, and a VMEbus access timeout

timer. The system controller also provides an arbitration

timeout if BBSY* is not seen within a specified period after

a BGOUT* signal is issued. This period is programmable

for 16 or 256 µs.

VMEbus REQUESTER — The microprocessor can

request and gain control of the bus using any of the VMEbus

request lines (BR3* to BR0*) under software control. The

requester can be programmed to operate in any of the

following modes:

Release-On-Request (ROR)

Release-When-Done (RWD)

VMEbus Capture and Hold (VCAP)

MAILBOXES — The VMEbus interface provides four

32-bit mailboxes, which are accessible from both the

microprocessor and the VMEbus providing interprocessor

communication. The mailboxes have the ability to interrupt

the microprocessor when accessed by theVMEbus.

INTERRUPT HANDLER — The interrupt handler

monitors, and can be programmed to respond to any or all

VMEbus IRQ* lines. All normal-process VMEbus-related

interrupts can be mapped to PCI INTA# or SERR#

interrupts. These include:

Mailbox interrupts

VMEbus interrupts

VMEbus interrupter IACK cycle (acknowledgment

of VMIVME-7700 VMEbus-issued interrupts)

All error processing VMEbus-related interrupts can be

mapped to PCI INTA# or SERR#. Note: PCI SERR#

initiates an SBC NMI. These include:

ACFAIL* interrupt

BERR* interrupt

SYSFAIL* interrupt

The interrupt handler has a corresponding STATUS/ID

register for each IRQ* interrupt. Once the handler receives

an IRQ*, it requests the VMEbus and, once granted, it

performs an IACK cycle for that level. Once the IACK cycle

is complete and the STATUS/ID is stored in the

corresponding ID register, an appropriate interrupt status bit

is set in an internal status register, and a PCI interrupt is

generated. The PCI interrupt can be mapped to PCI INTA#

or SERR#.

INTERRUPTER — Interrupts can be issued under

software control on any or all of the seven VMEbus interrupt

lines (IRQ7* to IRQ1*). A common ID register is associated

with all interrupt lines. During the interrupt acknowledge

cycle, the interrupter issues the ID to the interrupt handler.

The interrupter can be programmed to generate a PCI INTA#

or SERR# interrupt when a VMEbus interrupt handler

acknowledges a software-generated VMEbus interrupt.

- YOKOGAWA

- Energy Access

- Renewable Integration

- Energy Subsidies

- Energy and Water

- Net zero emission

- Energy Security

- Critical Minerals

- A-B

- petroleum

- Mine scale

- Energy and Gender

- Covid-19

- man-machine

- Reliance

- ADVANCED

- SEW

- ProSoft

- WATLOW

- Kongsberg

- FANUC

- VSD

- DCS

- PLC

- Sewage treatment

- cement

- Yaskawa

- Woodward

- BOSCH Rexroth

- MOOG

- General Electric

- American NI

- Rolls-Royce

- CTI

- Honeywell

- EMERSON

- Automobile market

- xYCOM

- Motorola

- architecture

- Industrial information

- New energy

- electricity

- Construction site

- HIMA

- ABB

- Rockwell

- Schneider Modicon

- Siemens

- MAN

- GE

- TRICONEX

- Control Wave

- ALSTOM

- AMAT

- STUDER

- KONGSBERG

- MOTOROLA

- DANAHER MOTION

- Bentley

- Galil

- EATON

- MOLEX

- Triconex

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- KOLLMORGEN

- Beijer

- Endress+Hauser

- schneider

- Foxboro

- KB

- REXROTH

- YAMAHA

- Johnson

- Westinghouse

- WAGO

- TOSHIBA

- TEKTRONIX

91

-

Kollmorgen S33GNNA-RNNM-00 - Brushless Servo Motor

-

Kollmorgen 6sm56-s3000-g-s3-1325 - Servo Motor

-

Kollmorgen AKM52K-CCCN2-00 - Servo Motor

-

Kollmorgen PSR3-230/75-21-202 - Power Supply

-

Kollmorgen akm24d-anc2r-00 - Servo Motor

-

Kollmorgen AKM22E-ANCNR-00 - Servo Motor

-

Kollmorgen S60300-550 - Servo Drive

-

Kollmorgen B-204-B-21 - Servomotor

-

Kollmorgen AKM21E-BNBN1-00 - Servo Motor

-

Kollmorgen TT2953-1010-B - DC Servo Motor

-

Kollmorgen pa8500 - Servo Power Supply

-

Kollmorgen BDS4A-210J-0001-207C2 - Servo Drive

-

Kollmorgen TTRB1-4234-3064-AA - DC Servo Motor

-

Kollmorgen MH-827-A-43 - Servo Motor

-

Kollmorgen AKM24D-ACBNR-OO - Servo Motor

-

Kollmorgen 00-01207-002 - Servo Disk DC Motor

-

Kollmorgen AKM21C-ANBNAB-00 - Servo Motor

-

Kollmorgen PSR3-208/50-01-003 - Power Supply

-

Kollmorgen 6SM56-S3000 - Servo Motor

-

Kollmorgen DBL3H00130-B3M-000-S40 - Servo Motor

-

Kollmorgen 6SN37L-4000 - Servo Motor

-

Kollmorgen AKM65K-ACCNR-00 - Servo motor

-

Kollmorgen 6SM56-L3000-G - Servo Motor

-

Kollmorgen AKMH43H-CCCNRE5K - Servo Motor

-

Kollmorgen PSR4/52858300 - Power Supply

-

Kollmorgen KBM-79H03-E03 - Direct Drive Rotary Motor

-

Kollmorgen AKM33E-ANCNDA00 - Servo Motor

-

Kollmorgen U9M4/9FA4T/M23 - ServoDisc DC Motor

-

Kollmorgen AKM13C-ANCNR-00 - Servo Motor

-

Kollmorgen AKM43L-ACD2CA00 - Servo Motor

-

Kollmorgen AKM54K-CCCN2-00 - Servo Motor

-

Kollmorgen M-605-B-B1-B3 - Servo Motor

-

Kollmorgen AKD-P00606-NBAN-0000 - Rotary Drive

-

Kollmorgen 6SM-37M-6.000 - Servo Motor

-

Kollmorgen A.F.031.5 - Sercos Interface Board

-

Kollmorgen 918974 5054 - Servo PWM

-

Kollmorgen U12M4 - ServoDisc DC Motor

-

Kollmorgen AKD-B00606-NBAN-0000 - Servo Drive

-

Kollmorgen MV65WKS-CE310/22PB - Servo Drive

-

Kollmorgen 65WKS-CE310/22PB - Servo Drive

-

Kollmorgen EM10-27 - Module

-

Kollmorgen S64001 - Servo Drive

-

Kollmorgen CR03200-000000 - Servo Drive

-

Kollmorgen 6SM57M-3000+G - Servo Motor

-

Kollmorgen BDS4 - Servo Drive

-

Kollmorgen AKD-P00306-NBEC-000 - Servo Drive

-

Kollmorgen AKD-B01206-NBAN-0000 - Servo Drive

-

Kollmorgen STP-57D301 - Stepper Motor

-

Kollmorgen 6SM37L-4.000 - Servo Motor

-

Kollmorgen 44-10193-001 - Circuit Board

-

Kollmorgen PRDR9SP24SHA-12 - Board

-

Kollmorgen PRD-AMPE25EA-00 - Servo Drive

-

Kollmorgen DBL3N00130-0R2-000-S40 - Servo Motor

-

Kollmorgen S406BA-SE - Servo Drive

-

Kollmorgen AKD-P00607-NBEI-0000 - Servo Drive

-

Kollmorgen AKD-P01207-NBEC-0000 - Servo Drive

-

Kollmorgen CR03550 - Servo Drive

-

Kollmorgen VSA24-0012/1804J-20-042E - Servo Drive

-

Kollmorgen N2-AKM23D-B2C-10L-5B-4-MF1-FT1E-C0 - Actuator

-

Kollmorgen 04S-M60/12-PB - Servo Drive

-

Kollmorgen H33NLHP-LNW-NS50 - Stepper Motor

-

Kollmorgen A-78771 - Interlock Board

-

Kollmorgen AKM43E-SSSSS-06 - Servo Motor

-

Kollmorgen AKD-P00607-NBEC-0000 - Servo Drive

-

Kollmorgen E21NCHT-LNN-NS-00 - Stepper Motor

-

Kollmorgen cr10704 - Servo Drive

-

Kollmorgen d101a-93-1215-001 - Motor

-

Kollmorgen BDS4A-203J-0001-EB202B21P - Servo Drive

-

Kollmorgen MCSS23-6432-002 - Connector

-

Kollmorgen AKD-P01207-NACC-D065 - Servo Drive

-

Kollmorgen CK-S200-IP-AC-TB - I/O Adapter and Connector

-

Kollmorgen CR10260 - Servo Drive

-

Kollmorgen EC3-AKM42G-C2R-70-04A-200-MP2-FC2-C0 - Actuator

-

Kollmorgen BDS5A-206-01010-205B2-030 - Servo Drive

-

Kollmorgen s2350-vts - Servo Drive

-

Kollmorgen AKM24D-ANC2DB-00 - Servo Motor

-

Kollmorgen E31NCHT-LNN-NS-01 - Stepper Motor

-

Kollmorgen PRD-0051AMPF-Y0 - Servo Board

-

Kollmorgen TB03500 - Module

-

Kollmorgen 60WKS-M240/06-PB - Servo Drive

-

Kollmorgen M21NRXC-LNN-NS-00 - Stepper Motor

-

Kollmorgen H-344H-0212 - Servo Motor

-

Kollmorgen MCSS08-3232-001 - Connector

-

Kollmorgen AKM33H-ANCNC-00 - Servo Motor

-

Kollmorgen PA-2800 - Power Supply

-

Kollmorgen MTC308C1-R1C1 - Servo Motor

-

Kollmorgen PRDR0091300Z-00 - Capacitor Board

-

Kollmorgen BDS4A-206J-0024/01502D79 - Servo Drive

-

Kollmorgen S20330-VTS - Servo Drive

-

Kollmorgen S20250-CNS - Servo Drive

-

Kollmorgen SBD2-20-1105-WO - Servo Drive Board

-

Kollmorgen M405-C-A1--E1 - Servo Motor

-

Kollmorgen PRD-PB805EDD-00 - Servo Drive

-

Kollmorgen 6SM57S-3.000-J-09-HA-IN - Servo Motor

-

Kollmorgen AKM33H-ANCNDA-00 - Servo Motor

-

Kollmorgen PCB-00030200-04 - PCB

-

Kollmorgen H22SSLB-LNN-NS-02 - Stepper Motor

-

Kollmorgen BJRL-20012-110001 - Module

-

Kollmorgen BDS4A-206J-0001404A - Servo Drive

-

Kollmorgen H-342-H-0802 - Servo Motor

-

Kollmorgen CR10561 - Servo Drive

-

Kollmorgen BDS5A-206-00010-205B2-030 - Servo Drive

-

Kollmorgen BDS5A-206-00010-207B-2-030 - Servo Drive

-

Kollmorgen mcss08-3224-001 - Connector

-

Kollmorgen M-207-B-23-B3 - Servo Motor

-

Kollmorgen PRD-0041200Z-S0 - Encoder/Resolver Card

-

Kollmorgen MH-225-G-61 - Motor

-

Kollmorgen MT308B1-T1C1 - Servo Motor

-

Kollmorgen BDS4A-240J-0001604C83 - Servo Drive

-

Kollmorgen 6SM57-S-3000 - Servo Motor

-

Kollmorgen N-T31V-15-5B-6-MF3-FT1E-C251 - Actuator

-

Kollmorgen PRD-0051AMPA-X0 - Servo Board

-

Kollmorgen CF-SS-RHGE-09 - Cable

-

Kollmorgen DIGIFAS7204 - Servo Drive

-

Kollmorgen S30101-NA - Servo Drive

-

Kollmorgen DIGIFAS7201 - Servo Drive

-

Kollmorgen PRD-0051AMPA-Y0 - Servo Board

-

Kollmorgen AKM23D-EFCNC-00 - Servo Motor

-

Kollmorgen SE10000 - Servo Drive

-

Kollmorgen PSR4/5A-112-0400 - Power Supply

-

Kollmorgen AKM31H-ANCNC-01 - Servo Motor

-

Kollmorgen M-203-B-93-027 - Servo Motor

-

Kollmorgen CP-SS-G1HE-05 - Connector

-

Kollmorgen AKM42G-ASCNR-02 - Servo Motor

-

Kollmorgen DBL4N00750-B3M-000-S40 - Servo Motor

-

Kollmorgen R3-BK23-152B-12-PL-ASE-BS115 - Actuator

-

Kollmorgen MH-427-B-61 - Motor

-

Kollmorgen cr06902 - Servo Drive