K-WANG

MOTOROLA MVME162 Embedded Controller

MOTOROLA MVME162 Embedded Controller

The complete user guide for the Motorola MVME162 series embedded controller (model 001-043) is developed from eight dimensions: manual basic information, hardware specifications, hardware configuration installation, operating instructions, functional modules, serial port interconnection, security compliance, and supporting resources. It is the core reference for the design, use, and development of this controller. The following is a detailed summary of the points:

Core hardware specifications

MVME162 is a dual high VME module, divided into 21 models (001-043). The core configuration revolves around a 25MHz 32-bit MC68LC040/MC68040 processor, both of which include 8KB cache and MMU. MC68040 also comes with a floating point coprocessor (FPU). The differences in core capacity among different models are DRAM capacity and whether they have SCSI/Ethernet/VMEBus interfaces. The core hardware specifications are shown in the table below:

table

Hardware Category Core Configuration Key Parameters/Remarks

Processor MC68LC040/MC68040 25MHz, 32-bit, former without FPU, latter with FPU

Main storage DRAM 1/4/8MB optional, with programmable parity check, 1MB for non interleaved architecture, 4/8MB for interleaved architecture

Static storage SRAM 512KB, with battery backup, worst-case backup for 200 days, no parity check

Read only/flash EPROM+Flash 4Mbit EPROM slot (JEDEC 32 pin PLCC); 1MB Flash (1 old board with 28F008SA, 4 new boards with 28F020)

Non volatile storage NVRAM+TOD clock Thompson MK48T08, 8K × 8 NVRAM with battery backup, TOD clock supports seconds/minutes/hours/days/months/years, BCD 24-hour clock

Timer/watchdog MCchip+VMEchip2 MCchip: 4 32-bit programmable timers (1 μ s resolution)+1 watchdog; VMEchip2: 2 32-bit programmable timers+1 watchdog

Power requirement: DC power supply+5V (± 5%): 3.5A typical, 4.5A maximum; +12Vdc (± 5%): 100mA maximum; -12Vdc (± 5%): 100mA maximum

Physical dimensions of dual height VME board: Board size: 233mm × 160mm × 17mm; with connector/panel: 262mm × 188mm × 20.32mm

Working environment temperature/humidity Working temperature: 0-70 ℃ (forced air cooling outlet temperature); Storage temperature: -40-85 ℃; Relative humidity: 5% -90% (non condensing)

Hardware configuration and installation

This chapter provides a detailed explanation of the unpacking, jumper configuration, and module installation steps for MVME162. The core operations must be carried out in a power-off state to avoid static electricity damage to the circuit. The core content includes:

Requirements for unpacking: If the packaging box is damaged, the carrier's agent must be present to unpack and inspect it, retain the packaging materials for storage/transportation, and avoid touching the integrated circuit area;

Jumper configuration: The board contains multiple configurable jumper caps, which are factory default configurations and can be modified according to needs. The core jumper functions are shown in the following table:

|Jumper number | Function | Factory configuration | Optional configuration|

|J1 | System Controller Selection | 1-2 Short Circuit (for VMEbus System Controller) | Remove Jumper (for Non System Controller)|

|J11 | Serial port 1/console clock | No jumper (asynchronous communication) | 1-2, 3-4 short circuit (synchronous external clock)|

|J12 | Serial port 2 clock | No jumper (asynchronous communication) | 1-2, 3-4 short circuit (synchronous external clock)|

|J20 | SRAM backup power supply | 1-3, 2-4 short circuit (VMEbus+5V backup power supply) | 3-5, 4-6 short circuit (onboard battery)|

|J21 | EPROM Capacity Selection | 2-3 Short Circuit (4Mbit, Only Available Specification) | -|

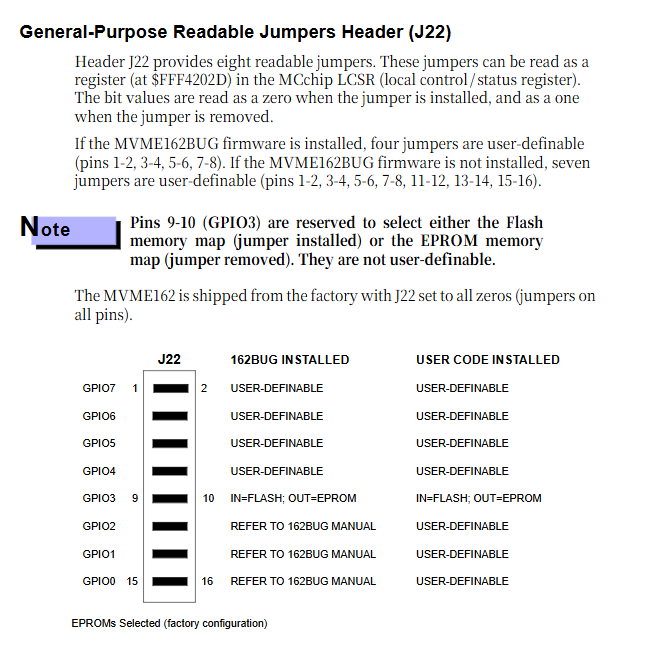

|J22 | Universal readable jumper | Fully short circuited (all 0) | Partially removed, corresponding register value is 1, GPO3 (9-10) is used to select Flash/EPROM|

SIM serial port module: Serial port 2 (Port B) is equipped with a SIM module through the J10 interface, supporting four types of DTE/DCE: EIA-232D/EIA-530. The module can be plugged and replaced, and the core model is SIM05-SIM08;

Module installation

IP modules: up to 4 can be installed, corresponding to J2/J3, J7/J8, J13/J14, J18/J19 interfaces, supporting dual size IP modules;

MVME162 board: If it is a system controller, it needs to be installed in slot 1 on the leftmost side of the VME chassis. The IACK/BG jumper in the slot needs to be removed and firmly connected to the P1/P2 backplane connector;

Transition module: MVME712 series transition module is required, only its serial ports 2/4 can be used, and 1/3 and printer ports are prohibited. This module cannot be used when configuring EIA-530;

System supporting requirements: To complete the MVME162 system setup, it is necessary to provide the system console terminal, disk drives and controllers, operating system, MVME712 transition module+P2/LCP2 adapter board and cables.

Operation instructions

This chapter introduces the front-end panel operations, memory mapping rules, software initialization, and reset operations of MVME162, which are the core basis for device use and program development

Front panel controls

Buttons: ABORT (S1) (Generate programmable interrupt after software enable, return 162Bug), RESET (S2) (Reset all devices on the board, if it is a system controller, drive SYSRESET *);

8 LED indicator lights: FAIL (red, BRDFAIL * activated), STAT (yellow, processor paused), RUN (green, local bus cycle executed), SCON (green, for VMEbus system controller), LAN (green, LAN chip is local bus master device), FUSE (green, LAN transceiver power is normal), SCSI (green, SCSI chip is local bus master device), VME (green, using VMEbus);

Memory mapping: divided into two types: local bus memory mapping and VMEbus memory mapping. The local bus address range is

00000000−

FFFFFFFF, The core partition includes programmable DRAM/SRAM/IP memory areas

FF800000−

FF9FFFFF's Flash/EPROM area

FFF00000−

FFFEFFFF's local I/O device area (including various registers)

FFFF0000−

VMEbus A16 area of FFFFFFFF; The local I/O device area includes core registers such as VMEchip2, MCchip, SCC, LAN, SCSI, IPIC, TOD clock, etc. The manual provides detailed definitions of the addresses, bit widths, and functions of each register;

BBRAM/TOD clock mapping: The 8KB NVRAM of MK48T08 is divided into user area, network area, system area, debugging area, configuration area (256B), TOD clock area (8B). The configuration area stores key information such as card serial number, Ethernet address, SCSI ID, etc., and the last byte is the checksum;

Software initialization: The 162Bug debugging firmware completes the default configuration of most control registers during power on/reset. If custom configuration is required, please refer to the M68040 manual and MVME162 programming reference guide; In a multi MPU system, only one MPU control register is allowed at a time to avoid conflicts;

Reset operation

System reset (SYSRESET *): triggered by the reset button, power on, watchdog timeout, and VMEchip2 LCSR bit, lasting at least 200ms and complying with the VMEbus specification;

Local Reset (LRST): a subset of system reset, with 5 triggering methods (watchdog timeout, reset key, GCSR bit, etc.) SYSRESET*、 Power on), the VMEbus master device can reset the local bus through GCSR, which carries risks and is only used in case of device failure.

Function module analysis

This chapter analyzes the working principles, interface specifications, and timing performance of each core module of MVME162 from the perspective of hardware architecture. The core content includes:

Local bus architecture: 32-bit synchronous bus, based on MC68040 bus, supports burst transmission and listening, bus arbitration is priority arbitration, and the priority of the main device from high to low is LAN (82596CA)>SCSI (53C710)>VMEbus>MPU;

Core storage module

DRAM: Controlled by MCchip, with programmable base address and capacity, parity errors can trigger interrupts/bus exceptions, requiring at least 10 initialization cycles;

SRAM: 512KB 32-bit, powered by Dallas DS1210S for battery backup, supporting dual backup of VMEbus+5V backup power supply and onboard battery. The onboard battery is RAYOVAC FB1225 (two BR1225 lithium batteries), which can be backed up for at least 2 years in a 40 ℃ power outage state;

Flash/EPROM: Bus conversion from 8-bit to 32-bit is implemented by MCchip, and reset code reading source (Flash/EPROM) is selected through GPIO of J22;

Communication and Expansion Interface

Dual serial ports: controlled by Zilog Z85230, serial port 1 is EIA-232-D DCE, and serial port 2 can be selected from EIA-232-D/EIA-530 DTE/DCE, supporting asynchronous (110B/s-38.4KB/s) and synchronous (SDLC/HDLC) protocols, and supporting CTS/DCD/RTS/DTR control signals;

Ethernet: controlled by Intel 82596CA, with 32-bit local bus DMA, the unique Ethernet address of the board is $08003E2xxxxx, stored on BBRAM and board labels, LAN DMA cannot access VMEbus to avoid buffer overflow;

SCSI: Controlled by NCR 53C710, with 32-bit local bus burst DMA, supports SCSI bus, and requires correct termination at both ends of the bus. The adapter board provides a termination resistor slot and fuse;

Industry Pack: Controlled by IPIC ASIC, supports 4 IP interfaces with 3M connectors, programmable memory/I/O space, and supports interrupt control;

VMEbus: Implemented by VMEchip2 ASIC, factory optional configuration, does not support on-site installation, supports A24/A32 addresses, D8/D16/D32 data, supports DMA burst transfer (D64/MBLT), provides system controller, interrupt handling, bus arbitration and other functions;

Local resources

Programmable timers: 4 MCchips+22 VMEchips, 32-bit, 1 μ s resolution, capable of generating periodic interrupts;

Watchdog timer: 1 each for MCchip and VMEchip2, working independently, timeout can trigger SYSRESET *, local reset, and board fault signals;

Hardware interrupts: VMEchip2 provides 8 software programmable hardware interrupts that can be triggered by software;

Local bus timeout: Both VMEchip2 and MCchip provide timeout function, with a timeout value of 8/64/256 μ s/infinite. After timeout, a TEA signal is sent to the main device. MCchip implements this function for boards without VMEbus;

Timing performance: The core is DRAM read and write cycles, with non interleaved DRAM read cycles of 4,2,2,2, interleaved DRAM read cycles of 4,1,1,1, and write cycles of 3,2,2 at 25MHz; EPROM/Flash cycle is 3-10 bus clock/byte, programmable configuration; The SCSI DMA transfer rate is 44MB/s (25MHz, no checksum, interleaved DRAM), and the LAN DMA transfer rate is 20MB/s (25MHz, no checksum).

Serial port interconnection specification

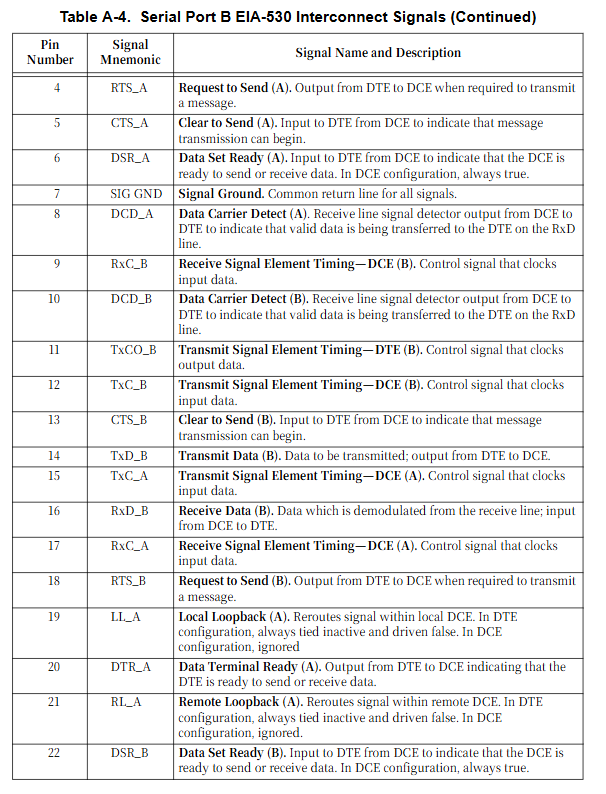

This chapter provides a detailed definition of the interconnection standard for MVME162 dual serial ports, supporting two specifications: EIA-232-D and EIA-530. The core content includes:

EIA-232-D: Single ended signal, DB25 interface, defined signal function for 25 pins, core uses TxD/RxD/RTS/CTS/DSR/DCD/DTR/SG, suitable for short distance transmission (recommended ≤ 15m), total load capacitance ≤ 2500pF, manual defines the electrical characteristics of transmitter/receiver (minimum output voltage ± 8.5V, input threshold ± 2.25V/± 0.75V);

EIA-530: Supports balanced/single ended signals, DB25 interface, upgraded to EIA-232-D, supports higher transmission rates, core signal is differential signal (such as TxD_A/TxD_B), manual defines the electrical characteristics of transmitter/receiver (differential output voltage ≥ 2.0V, input threshold ± 200mV);

Grounding requirements: The signal ground (Pin7) must be connected to complete the circuit loop; Use with caution the chassis ground (Pin1) to avoid current and data interference caused by different device ground potential differences. Only connect the signal ground to the chassis ground at one location (recommended on the computer side).

- YOKOGAWA

- Reliance

- ADVANCED

- SEW

- ProSoft

- WATLOW

- Kongsberg

- FANUC

- VSD

- DCS

- PLC

- man-machine

- Covid-19

- Energy and Gender

- Energy Access

- Renewable Integration

- Energy Subsidies

- Energy and Water

- Net zero emission

- Energy Security

- Critical Minerals

- A-B

- petroleum

- Mine scale

- Sewage treatment

- cement

- architecture

- Industrial information

- New energy

- Automobile market

- electricity

- Construction site

- HIMA

- ABB

- Rockwell

- Schneider Modicon

- Siemens

- xYCOM

- Yaskawa

- Woodward

- BOSCH Rexroth

- MOOG

- General Electric

- American NI

- Rolls-Royce

- CTI

- Honeywell

- EMERSON

- MAN

- GE

- TRICONEX

- Control Wave

- ALSTOM

- AMAT

- STUDER

- KONGSBERG

- MOTOROLA

- DANAHER MOTION

- Bentley

- Galil

- EATON

- MOLEX

- Triconex

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- KOLLMORGEN

- Beijer

- Endress+Hauser

- schneider

- Foxboro

- KB

- REXROTH

- YAMAHA

- Johnson

- Westinghouse

- WAGO

- TOSHIBA

- TEKTRONIX

- BENDER

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- XP POWER

- Baldor

- Meggitt

- SHINKAWA

- Other Brands

- other brands

- UniOP

- KUKA

- IBA

-

Metso XZB10025-011T12 - Moog Valve 9650962700

-

Metso XZB10025-010T12 - Moog Valve 9650965300

-

Metso-SP Transmitter Cable - Operating Unit with 10m Cable

-

Harkila Metso Hybrid - Hunting Jacket Willow Green

-

Metso ND8221/S1 - Neles Valve Positioner

-

Metso METSO10119 - ScreenCheck Component

-

Metso LK-2025 - Linkage Kit

-

Metso A416733 - IQweight External Air Gap Temperature Sensor

-

Metso RKC22MT - Automation Component

-

Metso A413281 - Automation Board

-

Metso LCP9HLY - Stainless Steel Enclosure

-

Metso NP704S/B1S1 - Pneumatic Positioner with I/P Converter

-

Metso BAH3 - Slurry Seal Type

-

Metso A413531-03 - PLC Module Chassis Rack

-

Metso P4610004 - MCAI Communicator Controller

-

Metso QN2AN03HDM - Quartz Valve Positioner Stonel

-

Metso RKW-352-XZ - Automation Component

-

Metso A4300081 - Kajaani LCD Display

-

Metso A428026 7B - Kajaani Rectifier Unit 1

-

Metso 202218 - Kajaani Sensor Power Supply SR 902660

-

Metso 9150 316SS CSTL - Jamesbury 150-2" BN50 Valve

-

Metso 81806 - IOP101 Module

-

Metso STOM000272 - Paper Bushing CR38

-

Metso 1975413 - Chain Hoist Links

-

Metso IMO G053-191597 - Minor Seal Kit

-

Metso VAL0087418 - Cylinder Valmet NTS6LV

-

Metso A413061 - DMU Board VPA 420355-4B

-

Metso P2620-80/25-100 - Automation Component

-

Metso VAL0035292 - Automation Component

-

Metso A413721 - Automation Component

-

Metso ST600 - Automation Component

-

Metso P4500001 - Automation Component

-

Metso SDBX/RA2 - CAT x KVM Extender

-

Metso D201126-DI8 - Digital Input Module

-

Metso D201189L - AI8H Analog Module

-

Metso NA004418 LK1016 - Wafersphere Actuator Mounting Bracket

-

Metso RKN172MTT - Repair Kit

-

Metso MM0311584 - Air Filter Kit RadialSeal

-

Metso 181517 - IOP301 Isolated Analog Input Module

-

Metso RAU3906506 - Automation Component

-

Metso 181208 - IOP332 Digital Input Module

-

Metso A413760 - AIF2C PCB Module

-

Metso 006 1089 36 - Shaft Bearing Seal

-

Metso A413046 - Automation Component

-

Metso VKJ650 - Automation Brake Component

-

Metso LK-1875 - Linkage Kit

-

Metso D201193L - FI4S24 Frequency Input Module

-

Metso D200533 - BIU82 Binary Input Module

-

Metso 500838-M1 - Impeller Pump Release Collar Assembly

-

Metso 2.00SB2ALUS19A - Pneumatic Cylinder 1.375 Stroke

-

Metso D201351 - RES Reserve Module

-

Metso A416100 - IQMoisture Spare Part Kit Halogen Lamp

-

Metso Slurry Pump - Back Liner

-

Metso 7088010042 - Bronze Lantern Ring

-

Metso IMC-101-M-SC - Industrial Media Converter

-

Voith S1-S1-CAM-ENCL - Metso Pump Cmare Housing & Bracket

-

Metso A4430726V1.1 - Kajaani Connection Box CI 4-9-10

-

Metso A413016 - NCU2 PLC Board

-

Metso D202213P - MBMT80 Base

-

Metso A413135 - AOU-4 Analog Output Board

-

Metso NP 724A - Pneumatic Valve Positioner

-

Metso A413246 - Automation Controller Module

-

Konaflex VKJ-650 - Disc Brake Set Pair

-

Metso WIN3096535D - Core Chuck

-

Metso D201380 - MBR Base with IBC & IPS

-

Metso D202213L - MBMT80 Base Module

-

Metso 181571 - IOP337 PLC Module

-

Metso MF0588336 - Main Hydraulic Filter

-

Metso 181504 - IOP303 RTD Input Module

-

Metso A413240 - PIC2 Board

-

Denver 566534PS - Case Liner Gland Side SRL Frame 2

-

Metso 181508 - IOP322 Digital Input Module 120V

-

Metso 181520 - IOP351 Relay Output Module Form A/B

-

Metso 181220 - IOP351 Relay Output Module

-

Metso A413150 - BOU 8 Binary Output Module

-

Metso 128400-M1 - Impeller

-

Metso D201379 - MBB Base with IBC & IPS

-

Metso 205181 - T/B MTD PRWSW Assembly

-

Metso QPX1C/K15 - Jamesbury Quadra-Powr X Actuator Valve

-

Harkila Metso Winter - Hunting Jacket Willow Green

-

Metso NE724A/A-L - Electro-Pneumatic Positioner

-

Metso PACP-100-80-31 916 - Automation Component

-

Metso 81814 - Automation Component

-

Metso ER-12-01-M-CT - Automation Board

-

Metso ELO24 - Automation Board

-

Metso A413000 - Valmet Neles CPU PLC Board

-

Metso XL-2213-0525 - Mainframe Bushing

-

Metso D100097 - ECR Extension Module

-

Metso 804511 - Filter Housing Assembly

-

Metso S420154 - Automation Rack Chassis

-

Metso M851232 - Automation Module

-

Metso D100532 02 - Automation Board

-

Neles QPX1C/M - Ball Valve with Quadra-Powr X Actuator

-

Metso 181535 - IOP322 Isolated Analog Output Module

-

Metso RKN-184-XTZ - Ball Valve Seat Repair Kit 4"

-

Metso N22022621 - Metal Plate

-

Metso 181560 - IOP341 Positioner Module

-

Metso LT 1213 S - Filter Service Kit for CAT C12 Engine

-

Aq-Matic 0032-99000 - Valve Diaphragm

-

Metso D200535 - BOU8 Output Board

-

Metso EDS-305-M-SC - Ethernet Switch

-

Metso 80424 - IOP110 Analog Output Module

-

Metso IOP351 - Relay Output Module Form A/B

-

Metso 181572 - IOP342 Module

-

Metso 1-1-2A3600TT - Ball Valve 1.5"

-

Metso A413154 - BOU8-4 Output Module

-

Metso A413140 - Valmet BIU 8 Board

-

Metso D201139 - IPS Power Supply type DDC7940

-

Metso PGH P411382-2000 - Metal Feed/Filtrate Hose

-

Valmet 503201404 - Automation Board

-

Metso 181507 - IOP331 Controller Module

-

Metso A413141 - BIU82 Binary Input Module

-

Metso KSD7447686 - Pneumatic Cylinder 5" Bore

-

Metso APL3003850 - Automation Component

-

Metso D201135L - Automation Controller

-

Metso A413125 - AIU8 Analog Input Module

-

Metso A413325 - IPU Power Unit

-

Metso 181573 - IOP346 PLC Module

-

Metso A413143 - BIU84 Binary Output Module Card

-

Metso A413152 - BOU82 Output Module

-

Metso PDP603 - Distributed Processing Unit 181555

-

Metso PDP601 - Distributed Processing Unit 181555

-

Metso A413040 - DCS Board DCU

-

Metso A413082 - CPU Processor Module

-

Valmet TI4W3 - Temperature Input Module

-

Valmet FI4S24 - Frequency Input Module

-

Metso 1064669615 - Fulcrum Bar

-

Valmet 181206 - IOP330 Digital Input Module

KONG JIANG

Add: Jimei North Road, Jimei District, Xiamen, Fujian, China

Tell:+86-15305925923