K-WANG

GE VMIVME-3115-010 32-Channel 12-bit Analog Output Board

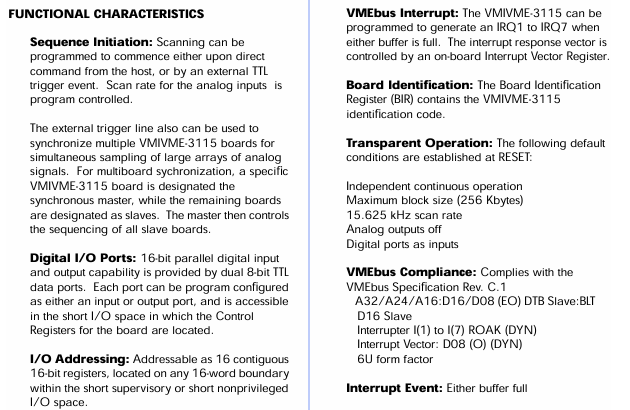

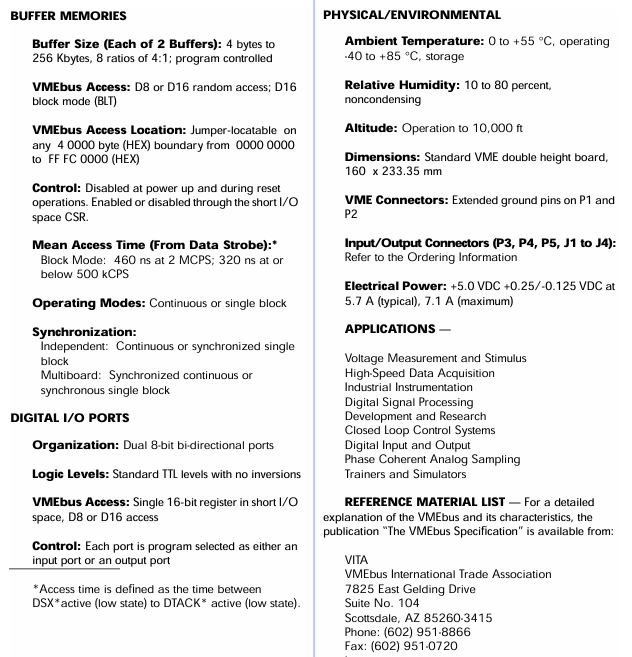

Dual-ported data memory, on-board timers, and a program-controlled bus interrupter enables the VMIVME-3115 board to support extensive analog input and output traffic with minimum involvement of the host processor.

GE VMIVME-3115-010 32-Channel 12-bit Analog Output Board

ANALOG INPUTS

Dual-ported data memory, on-board timers, and a program-controlled bus interrupter enables the VMIVME-3115 board to support extensive analog input and output traffic with minimum involvement of the host processor.

Sample-and-hold input amplifiers provide “snapshot” simultaneous sampling of all analog inputs at aggregate sample rates up to 2 MHz, and virtually eliminate time skewing between input channels. The VMIVME-3115 supports both independent and multiboard synchronization. Dual analog outputs enable the board to “close the loop” in system servo applications.

memory to the VME host. Total memory space occupied by the board is 256 Kbytes, and can be program located on any 4 0000 byte (HEX) boundary in the VMEbus memory space. The VMIVME-3115 buffers can be removed (masked) from VMEbus memory by a CSR control bit.

I/O Address Selection: Board address in the short I/O space is selected by on-board field selectable jumpers.

Operation is supported in any slot except slot 1.

6U form factor

Interrupt Event: Either buffer full

- YOKOGAWA

- Reliance

- ADVANCED

- SEW

- ProSoft

- WATLOW

- Kongsberg

- FANUC

- VSD

- DCS

- PLC

- man-machine

- Covid-19

- Energy and Gender

- Energy Access

- Renewable Integration

- Energy Subsidies

- Energy and Water

- Net zero emission

- Energy Security

- Critical Minerals

- A-B

- petroleum

- Mine scale

- Sewage treatment

- cement

- architecture

- Industrial information

- New energy

- Automobile market

- electricity

- Construction site

- HIMA

- ABB

- Rockwell

- Schneider Modicon

- Siemens

- xYCOM

- Yaskawa

- Woodward

- BOSCH Rexroth

- MOOG

- General Electric

- American NI

- Rolls-Royce

- CTI

- Honeywell

- EMERSON

- MAN

- GE

- TRICONEX

- Control Wave

- ALSTOM

- AMAT

- STUDER

- KONGSBERG

- MOTOROLA

- DANAHER MOTION

- Bentley

- Galil

- EATON

- MOLEX

- Triconex

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- KOLLMORGEN

- Beijer

- Endress+Hauser

- schneider

- Foxboro

- KB

- REXROTH

- YAMAHA

- Johnson

- Westinghouse

- WAGO

- TOSHIBA

- TEKTRONIX

- BENDER

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- XP POWER

- Baldor

- Meggitt

- SHINKAWA

- Other Brands

- other brands

- UniOP

- KUKA

- IBA

-

ABB G3ENa HENF450268R2 Industrial Automation Control Module High Performance Processing and Distributed System Interface Unit

-

ABB P5EAa HENF206350R2 Industrial Automation Control Module Advanced Processing and High Reliability System Interface Unit

-

ABB O3EC HENF442581R1 Industrial Automation Control Module High Precision Signal Processing and Distributed System Interface Unit

-

ABB O3EHa HENF315087R2 Industrial Automation Control Module Advanced Signal Processing and System Interface Unit

-

ABB E3ED Industrial Automation Control Module High Stability Signal Processing and Distributed System Interface Unit

-

ABB O3ED Industrial Automation Control Module Signal Processing and Distributed System Interface Unit

-

ABB E3EP HENF315276R1 Industrial Automation Control Module High Precision Signal Processing and System Interface Unit

-

ABB O3EGb HENF315118R2 Industrial Automation Control Module Advanced Signal Processing and System Interface Unit

-

ABB O3ES HENF445789R1 Industrial Automation Control Module Advanced Signal Processing and Distributed System Interface Unit

-

ABB E3EB HENF315129R1 Industrial Automation Control Module High Stability Signal Processing Unit

-

ABB G3ESa HENF318736R1 Industrial Control Module Advanced Automation System Interface Processing Unit

-

ABB 8025-235 Industrial Control and Measurement Module Automation Signal Processing Unit

-

ABB REG216 Industrial Generator Protection and Control System Advanced Power Automation Relay Unit

-

ABB PU512V2 3BUR001401R1 Industrial Processor Unit High Performance Automation Control Module

-

ABB LDMUI-001 61320946C Industrial Drive Control Interface Module High Performance Automation Communication Unit

-

ABB 216NG61A HESG441633R1 HESG216875/K Industrial Control Module Advanced Automation Processing Unit System Interface

-

ABB PFTL201C 50KN 3BSE007913R50 High Precision Load Cell Industrial Tension Measurement and Force Control Sensor Unit

-

ABB RED670 High Performance Line Differential Protection Relay Industrial Power System Protection Unit

-

ABB PP825A 3BSE042240R3 Industrial Panel Controller Advanced Automation HMI Processing Unit

-

ABB SCYC51020 58052582/G Industrial Control and Communication Module High Stability System Interface Unit

-

ABB AO2000 LS25 Industrial Gas Analyzer System High Precision Emission Monitoring and Process Control Unit

-

ABB LM80 Industrial Measurement and Signal Processing Module Automation System Data Acquisition Unit

-

ABB PFEA113-20 3BSE028144R0020 Industrial Tension Control Module High Precision Measurement Unit

-

ABB PM803F 3BDH000530R1 Industrial Controller CPU Automation System Processing Unit

-

ABB SD822 3BSC610038R1 Power Supply Module Industrial Automation System Stable Energy Unit

-

ABB PCD235B1101 3BHE032025R1101 Industrial Control Module High Performance Automation Processing Unit

-

ABB AZ20/112112221112E/STD Industrial Gas Analyzer Control and Monitoring System High Precision Measurement Unit

-

ABB KP3000 Advanced Industrial HMI Panel Operator Control Interface System Unit

-

ABB KP2500 Industrial HMI Operator Panel Human Machine Interface Control Display Unit

-

ABB UFD203A101 3BHE019361R0101 Industrial Interface Control Module Automation Communication Unit

-

ABB GVC736CE101 3BHE039203R0101 Industrial Drive Control Processing Unit High Performance Automation Controller

-

ABB UAD142A01 3BHE012551R0001 Industrial Control and Automation Interface Module High Stability Processing Unit

-

GE HE693STP110 Stepper Motor Control Module for Industrial PLC Systems

-

GE HE693STP104AX Stepper Control Module for PLC Automation System

-

GE DS200TCQAG1BHF Turbine Control Module

-

GE DS200ADGIH1AAA Analog Input Control Board

-

ABB CAI04 Analog Input Module for Industrial Automation System Signal Acquisition and Process Control Interface Unit Replacement

-

ABB FET3251C0P184C0H2 Industrial Control Interface Module for Automation System Signal Processing and Power Management Unit Replacement

-

ABB 5SHY35L4503 IGCT Power Module for Industrial Drive System Inverter Control and High Power Conversion Unit Replacement

-

ABB PM866-2 3BSE050201R1 AC 800M Controller CPU Module for Industrial Automation System Control Processing and Distributed Control System Core Unit

-

ABB CP405 A0 1SAP500405R0001 HMI Touch Panel for Industrial Automation Operator Interface Display Control and Monitoring System

-

ABB R474A11XE HAFAABAAABE1BCA1XE Power Supply Module for Industrial Automation System Control Cabinet Energy Distribution and Interface Support Unit

-

GUTOR OP6257 Industrial Power Control Module | Reliable UPS System Component

-

ABB REF542PLUS 1VCR007346 Protection Relay for Substation Automation Power Distribution Control and Electrical Fault Protection System

-

ABB REF542PLUS 1VCF752000 Protection Relay for Substation Automation Power System Control and Electrical Fault Detection Unit

-

ABB PPD113B03-26-100100 3BHE023584R2625 Drive Control Board for Industrial Automation Excitation System and Power Electronics Control Module

-

ABB PCD232A 3BHE022293R0101 Industrial Drive Control Processing Module Power Electronics Interface Unit

-

ABB PFEA113-65 3BSE050092R65 Tension Control Module Industrial Automation Measurement Unit

-

ABB XVC767AE102 3BHB007209R0102 Industrial Drive Control Board Power Electronics System Module

-

ABB CI857K01 3BSE018144R1 Communication Interface Module for Industrial Automation System Control Network Integration and Data Exchange Gateway Unit

-

ABB 3ASC25H219B DATX133 Advanced Signal Interface Module for Industrial Automation System Multi-Channel Communication and Control Data Optimization Unit

-

ABB 3ASC25H214 DATX130 High-Speed Signal Interface Module for Industrial Automation System Communication Upgrade and Control Data Processing Unit

-

ABB 3ASC25H208 DATX100 Signal Interface Module for Industrial Automation System Communication Processing and Control Data Exchange Unit

-

ABB 3ASC25H204 DAPU100 Data Processing Unit for Industrial Automation System Control Coordination and High-Speed System Data Management Module

-

ABB 3ASC25H216A DATX132 Signal Interface Module for Industrial Automation System Control Expansion and High-Speed Data Communication Unit

-

ABB LWN2660-6 Power Supply and Network Interface Module for Industrial Automation System Control Cabinet Energy Distribution and Communication Support Unit

-

ABB ICSE08B5 FPR3346501R1012 Control and Signal Processing Module for Industrial Automation System Interface and System Expansion Unit

-

ABB 1MRK00008-KB Protection and Measurement Module for Power System Relay Control Industrial Substation Automation Unit

-

ABB UAD155A0111 3BHE029110R0111 Interface Module for Industrial Automation System Communication Control and Signal Processing Unit

-

ABB PM511V08 3BSE011180R1 Processor Unit for ABB Industrial Automation Control System CPU Module High Performance PLC and DCS Controller Unit

-

ABB PU515A 3BSE032401R1 Processor Unit for ABB Industrial Automation System Control Processing and High Performance PLC System Core Module

-

ABB TU810V1 3BSE013230R1 Terminal Unit for ABB S800 I/O System Industrial Automation Module Connection and Signal Interface Base Unit

-

ABB XO08R2 1SBP260109R1001 Digital Output Module for ABB PLC System Industrial Automation I/O Control Expansion Unit

-

ABB 3BHL000986P0006 Drive Control Power Module for Industrial Converter System High Power Automation and Motor Drive Control Unit

-

ABB SC540 3BSE006096R1 Control System Module for Industrial Automation PLC DCS Control and System Communication Processing Unit

-

ABB 5SHY4045L0001 IGBT Power Module 3BHB018162R0001 3BHE009681R0101 GVC750BE101 for High Power Industrial Drive and Converter Systems

-

ABB P4LQA HENF209736R0003 Control Interface Module for Industrial Automation System Signal Processing and System Integration Unit

-

ABB FENA-11 Ethernet Adapter Module for ABB Drives Industrial Communication Interface and Network Control Unit

-

ABB COM0003 2RAA005844A0006A Communication Processor Module for Industrial Automation System Network Control and Data Exchange Unit

-

ABB AIM0006 2RCA021397A0001F Communication Interface Module for Industrial Automation System Integration and Data Exchange Unit

-

ABB S-073N 3BHB009884R0021 Drive Control Module for ABB High Power Converter and Industrial Drive System Power Interface Unit

-

ABB REF615E Feeder Protection Relay HBFHAEAGNCA1BNN1XE Intelligent Protection Device for Power Distribution and Electrical Automation Systems

-

Meggitt C327845-11 Industrial Control Module | High Reliability Automation Component

-

ABB TP830 3BSE018114R1 Industrial Operator Panel HMI Interface Unit Automation Control Display Module

-

ABB DSAI146 3BSE007949R1 Industrial Analog Input Module Automation System Signal Interface Unit

-

ABB 5SHX2645L0004 3BHL000389P0104 IGBT Power Module for High-Power Industrial Drive System and ABB Converter Control Unit

-

ABB LC-608 Industrial Logic Control Module for ABB Automation System Interface Signal Processing and Control Integration Unit

-

ABB TK803V018 3BSC950130R1 System Interface Module for ABB DCS Automation Network Configuration and Industrial Control Support Unit

-

ABB RF522 3BSE000743R1 Communication Interface Module for ABB DCS System Network Node and Industrial Automation Control Integration Unit

-

ABB DSRF197 3BSE019297R1 Communication Interface Module for ABB DCS Industrial Automation System Signal and Network Control Unit

-

ABB DSBC176 3BSE019216R1 Bus Extender Board Industrial Communication Module for ABB DCS and PLC System Network Expansion Unit

-

ABB DSAO120A 3BSE018293R1 Analog Output Module Industrial Control I/O Unit for ABB DCS Automation System Process Control

-

ABB DSDP170 57160001-ADF Distributed I/O Processing Module for ABB DCS Automation System Expansion and Control Integratio

-

ABB DSDO115A 3BSE018298R1 Digital Output Module Industrial Control I/O Unit for ABB DCS Automation System

-

ABB DSDI110AV1 3BSE018295R1 Digital Input Module Industrial I/O Unit for ABB DCS Automation System Signal Acquisition

-

ABB 5SHY3545L0010 3BHB013088R0001 GVC750BE101 High Power IGBT Module for ABB Industrial Drive and Inverter System

-

ABB 81943A041-1 Industrial System Expansion Interface Module for ABB Automation and Control System Integration Unit

-

ABB SA168 3BSE003389R1 Signal Processing Module Industrial Analog Input Interface Unit for ABB Automation System

-

ABB PM865K01 3BSE031151R1 AC 800M Controller PLC Central Processing Unit Industrial Automation Control Module

-

ABB 5SHY3545L0016 3BHB020720R0002 GVC736BE101 IGBT Power Module High Power Inverter Module for ABB Drive System

-

ABB TP853 3BSE018126R1 HMI Operator Panel Industrial Control Touch Display Unit for ABB Automation System

-

ABB REM545AG228AAAA Advanced Protection Relay Industrial Power System Automation Control Device

-

ABB CI626A 3BSE005029R1 Industrial Communication Interface Module Distributed Control System Unit

-

ABB NDCU-12C Industrial Drive Control Unit Automation System Communication Module

-

ABB REM615C_D HCMJAEADAND2BNN1CD Protection and Control Relay Industrial Power System Automation Device

-

ABB IBA 940143201 Industrial Bus Adapter Module Automation Communication Interface Unit

-

ABB PFSK151 3BSE018876R1 Industrial Signal Processing Control Module Automation System Unit

-

ABB IDPG 940128102 Industrial Digital Power Control Module Automation System Component

-

ABB OCAH 940181103 Industrial System Interface Module for ABB DCS Communication and Signal Adaptation Unit

-

ABB OCAHG 492838402 Industrial Communication Interface Module for ABB DCS Control System Integration Unit

-

ABB PPD539 A102 3BHE039770R0102 Process Control Unit Industrial Automation Controller Module for ABB System

-

ABB PP825 3BSE042240R1 Basic HMI Operator Panel Industrial Control Display Unit for ABB Automation System

-

ABB TP857 3BSE030192R1 HMI Touch Panel Industrial Operator Interface Display Unit for ABB Automation System

-

ABB PP865A 3BSE042236R2 HMI Operator Panel Industrial Human Machine Interface Display Unit for ABB Control System

-

ABB SCYC51020 58052582H Drive Control Interface Board Industrial Inverter Communication Module

-

ABB SCYC51010 58052515G Drive Control Interface Board Industrial Inverter Signal Interface Unit

-

ABB CB801 3BSE042245R1 Control Board Industrial Drive System Central Control Unit for ABB IGBT Inverter System

-

ABB SCYC51090 58053899E IGBT Protection Control Board Industrial Drive Protection Unit for ABB Inverter System

-

ABB SCYC51040 58052680E Gate Driver Control Board Industrial IGBT Drive Control Unit for ABB Power System

-

ABB 5SHY4045L0001 3BHB018162R0001 High Power IGBT Module Industrial Drive Inverter Power Semiconductor Device

-

ABB 5SHY6545L0001 AC10272001R0101 5SXE10-0181 High Power Semiconductor Module Industrial Drive Control Component

-

ABB RMU811 Remote Monitoring Unit Industrial Automation Communication and Control Module

-

ABB RFO810 Industrial Control Module High-Performance Automation System Component

-

ABB CS31 Modular Control System Industrial Automation Communication Bus Module

-

ABB TVOC-2-240 1SFA664001R1001 Arc Fault Detection System Industrial Safety Monitoring Device

-

ABB SDCS-AMC-CLAS2 Advanced Control Module Industrial Drive Automation System Component

-

ABB LDSTA-01 Distributed Control System Module Industrial Automation Controller

-

ABB 07AC91F / 07AC91H GJR5252300R3101 Control Module Industrial Automation Controller Unit for ABB System

-

ABB TB711F 3BDH000365R0001 Terminal Block Module Industrial Wiring Interface Unit for ABB Freelance System

-

ABB CM772F 3BDH000368R0001 Communication Module Industrial Network Interface Unit for ABB Freelance Control System

-

ABB PM783F 3BDH000364R0002 Freelance Controller CPU Module High Performance Industrial Automation Control Processor Unit

-

ABB TU715F 3BDH000378R0001 & TB711F 3BDH000365R0001 Terminal Unit Industrial Wiring Interface Module for ABB Freelance System

-

ABB DC732F 3BDH000375R0001 Power Supply Module Industrial Automation System Power Unit for ABB Freelance Control System

-

ABB TTH300 Temperature Transmitter High Precision Industrial Temperature Measurement Device for Process Automation

-

ABB PFEA111-65 3BSE050091R65 Tension Controller High Precision Web Tension Control System for Industrial Automation

-

ABB UNS3670A-Z V2 HIEE205011R0002 Drive Control Board High Performance Industrial Power Control and Automation Unit

-

ABB RC527 3BSE008154R1 Communication Interface Module Industrial Network Integration Unit for Automation Systems

-

ABB 5SHY5055L0002 3BHE019719R0101 GVC736BE101 High Power IGBT Module Industrial Drive and Power Electronics Unit

KONG JIANG

Add: Jimei North Road, Jimei District, Xiamen, Fujian, China

Tell:+86-15305925923