+086-15305925923

K-WANG

Service expert in industrial control field!

Product

Article

NameDescriptionContent

Adequate Inventory, Timely Service

pursuit of excellence

Ship control system

Equipment control system

Power monitoring system

Current position:

新闻动态

newS

Brand

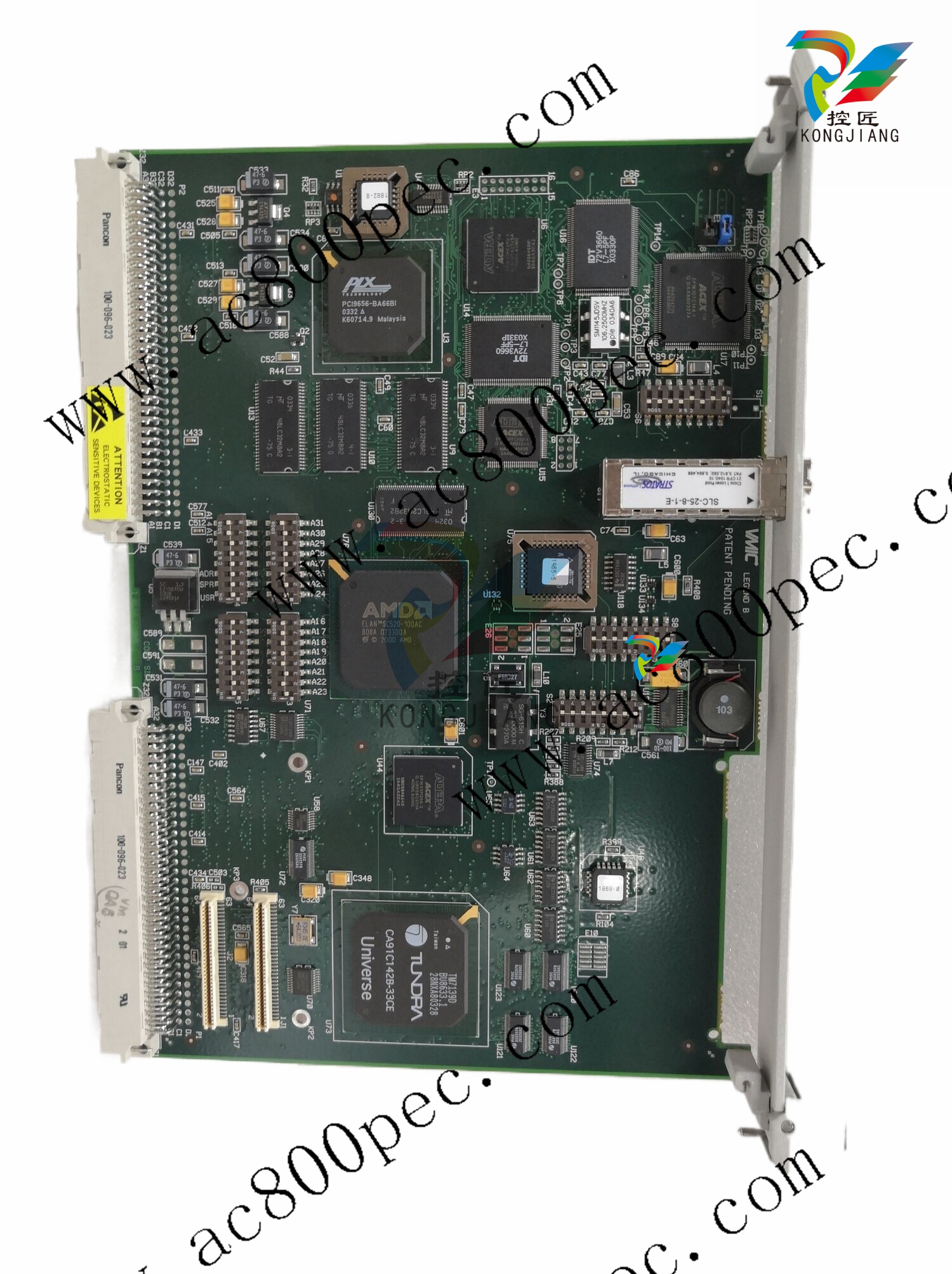

GE VMIVME-5565 Ultrahigh-Speed Fiber-Optic Reflective Memory with Interrupts

GE VMIVME-5565 Ultrahigh-Speed Fiber-Optic Reflective Memory with Interrupts

GE VMIVME-5565 Ultrahigh-Speed Fiber-Optic Reflective Memory with Interrupts

The VMIVME-7807/VME-7807RC provide a programmable Watchdog Timer (WDT)

which can be used to reset the system if software integrity fails.

WDT Control Status Register (WCSR)

The WDT is controlled and monitored by the WDT Control Status Register (WCSR)

which is located at offset 0x08 from the address in BAR2. The mapping of the bits in

this register are as follows:

The “WDT Timeout Select” field is used to select the timeout value of the Watchdog

Timer as follows:

The “SERR/RST Select” bit is used to select whether the WDT generates an SERR# on

the local PCI bus or a system reset. If this bit is set to “0”, the WDT will generate a

system reset. Otherwise, the WDT will make the local PCI bus SERR# signal active.

The “WDT Enable” bit is used to enable the Watchdog Timer function. This bit must

be set to “1” in order for the Watchdog Timer to function. Note that since all registers

default to zero after reset, the Watchdog Timer is always disabled after a reset. The

Watchdog Timer must be re-enabled by the application software after reset in order

for the Watchdog Timer to continue to operate. Once the Watchdog Timer is enabled,

the application software must refresh the Watchdog Timer within the selected timeout

period to prevent a reset or SERR# from being generated. The Watchdog Timer is

Field Bits Read or Write

SERR/RST Select WCSR[16] R/W

WDT Timeout Select WCSR[10..8] R/W

WDT Enable WCSR[0] R/W

All of these bits default to “0” after system reset. All other bits are reserved.

Timeout WCSR[10] WCSR[9] WCSR[8]

135s 0 0 0

33.6s 0 0 1

2.1s 0 1 0

524ms 0 1 1

262ms 1 0 0

131ms 1 0 1

32.768ms 1 1 0

2.048ms 1 1 1

The following table shows the register definitions for the VMIVME-7807/

VME-7807RC (offset from BAR0).

Please refer to Table 3-1, “PCI Configuration Space Registers,” on page 47 for more

information concerning BAR0.

Table 3-2 Register Definitions Offset From BAR0

Register Name Offset

VMECOMM 0x00

Bit Name Bit Definition

MEC_SEL 0 Master big-endian enable bit 1=Big Endian,

0=Little Endian bit

SEC_SEL 1 Slave Big-Endian enable bit 1=Big Endian,

0=Little Endian

ABLE 2 Auxiliary BERR logic enable bit

1=Aux. BERR enabled 0=Aux. BERR disabled

BTO 3 Bus error timer enabled 1=enabled, 0=disabled

BTOV [1:0] 5:4 Timeout value

00 - 16μs

01 - 64μs

10 -256μs

11 - 1.00ms

BERRI 6 BERR interrupt enable 1=Interrupt enabled

0=Interrupt disabled

BERRST 7 BERR status read/clear bit

1=Clear BERR status, 0=Do nothing

SFENA 8 Enables generation of VME SYSFAIL upon

WDT timeout

1= Enable SYSFAIL generation, 0=Disable

Unused 9 Not Used

BPENA 10 Endian conversion bypass bit

1=bypass, 0=Not bypassed

VBENA 11 VME enable bit (VBENA)

1 = enabled, 0 = disabled

Unused 31:12 Not Used

VBAM 0x04

VME_ADDR 5:0 Latched VME Address Modifier

Unused 31:6 Not Used

SEC_SEL 0x001

VBAR 0x08

VME_ADDR All Latched VME Address

- YOKOGAWA

- Reliance

- ADVANCED

- SEW

- ProSoft

- WATLOW

- Kongsberg

- FANUC

- VSD

- DCS

- PLC

- man-machine

- Covid-19

- Energy and Gender

- Energy Access

- Renewable Integration

- Energy Subsidies

- Energy and Water

- Net zero emission

- Energy Security

- Critical Minerals

- A-B

- petroleum

- Mine scale

- Sewage treatment

- cement

- architecture

- Industrial information

- New energy

- Automobile market

- electricity

- Construction site

- HIMA

- ABB

- Rockwell

- Schneider Modicon

- Siemens

- xYCOM

- Yaskawa

- Woodward

- BOSCH Rexroth

- MOOG

- General Electric

- American NI

- Rolls-Royce

- CTI

- Honeywell

- EMERSON

- MAN

- GE

- TRICONEX

- Control Wave

- ALSTOM

- AMAT

- STUDER

- KONGSBERG

- MOTOROLA

- DANAHER MOTION

- Bentley

- Galil

- EATON

- MOLEX

- Triconex

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- KOLLMORGEN

- Beijer

- Endress+Hauser

- schneider

- Foxboro

- KB

- REXROTH

- YAMAHA

- Johnson

- Westinghouse

- WAGO

- TOSHIBA

- TEKTRONIX

- BENDER

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- XP POWER

- Baldor

- Meggitt

- SHINKAWA

- Other Brands

- other brands

- UniOP

- KUKA

- IBA

91

-

ABB 5SHX1445H0002 Power Semiconductor Module

-

ABB CI853-1 Communication Interface Module

-

ABB CI858-1 Communication Interface Module

-

ABB PM861K01 Processor Unit

-

ABB REM610 Motor Protection Relay

-

ABB 5SDF1045H0002 Power Semiconductor Module

-

Lilaas R01TS10A0H03-00 Marine Control Lever Module

-

Metso 1H13767C-3 - Paper Pinion Hand Guide Bevel

-

Metso LK-2101 - Linkage Kit

-

Metso A413510 - Rack Enclosure 21 Slots

-

Metso ND9106HU-K - Intelligent Valve Controller

-

Metso D201190L - AO4H Analog Module

-

Metso WIN1011187 - Top Slitter Assembly

-

Metso 251920 - Automation Component

-

Metso LK-1871 - Linkage Kit

-

Metso SE200N529 - XP Power Supply 115/230 VAC

-

Metso Shadow Brown Fleece - Harkila Half Zip Sweater

-

Metso DI8P - Valmet Digital Input Module

-

Metso DO8S0 - Valmet Digital Output Module

-

Metso AO8C - Valmet Analog Output Module

-

Metso AO4H - Valmet Analog Output Module

-

Metso AI8C - Valmet Analog Input Module

-

Metso PDCF2529 - Shaft Sleeve

-

Metso ST2.8 - Lokotrack Owners Manual & Parts Book

-

Metso 500836-M1 - Impeller Pump Release Collar Assembly

-

Metso RKN 33 XT - Valve Service Kit Pack

-

Metso PDCH2539 - Shaft Sleeve

-

Metso LK-2017 - Actuator Linkage

-

Metso N88409030 - Hammer Screw Jaw Crusher M48X970

-

Metso 181538 - IOP365 Isolated Analog Input Module

-

Metso 10691-04 - Charging Kit Olear/Parker

-

Metso QX4SB02SDM - Automation Component

-

Metso VAL0062567 - Pneumatic Cylinder 250 Psi

-

Harkila Metso Full Zip - Fleece Jacket Willow Green

-

Metso AM1-389 829-0010-218 - Bracket for 3+4 in Ball Valve

-

Metso D200467 - IO Rack

-

Metso RKN-359XT - Repair Kit

-

Metso 2.00SB2HKT27A6 - Parker Pneumatic Cylinder

-

Metso D100306 - AIF2mV GEB Module

-

Metso A413757 - AOR4C GEB Module

-

Metso A413754 - AIR8H GEB Module

-

Metso A413767 - AOF2V GEB Module

-

Metso A413742 - BIR82 GEB Module

-

Metso A413744 - BOR82 GEB Module

-

Metso A413753 - AIR8V GEB Module

-

Metso A413752 - AIR8C GEB Module

-

Metso 96511900 - Hydraulic Filter

-

Metso IOP334 - Isolated Digital Input Module

-

Metso 1003894081 - High Flow Oil Filter Cartridge

-

Metso H035506 - Ball Valve Seat Set Kit

-

Metso PDCH2680 - Shaft Sleeve

-

Metso LK-937 - Linkage Kit

-

Metso VAL0353763 - Valmet Pneumatic Cylinder 250PSI

-

Metso APL3037188 - Hydraulic Cylinder 2" Bore

-

Metso 181540 - IOP307 Isolated Analog Input Module

-

Metso LK-2032 - Linkage Kit

-

Metso VAL0207205 - Valmet Automation Power Supply

-

Metso PDCF2680 - Shaft Sleeve

-

Metso 422244-1A - GMB Relay Module Board

-

Metso VAL0356906 - Paper Pneumatic Cylinder

-

Metso RKW-355TT - Jamesbury Repair Kit 8in

-

Metso QN2SP02SXM-BSF - Quartz Valve Control Stonel

-

Metso D201134 - AI8 Analog Input Module

-

Metso APL3032501 - Automation Component

-

Metso D201784L - MBM Backplane

-

Metso M851121 - DMU M2 Module

-

Metso A413310 - Valmet Neles VPU Power Unit

-

Sarianna Metso The Serekh Texts - Hardcover Book

-

Metso 5044i9PS - Pump Impeller

-

Metso 181575 - IOP345 Overspeed Trip Module

-

Metso RKQ-66 - Jamesbury Actuator Diaphragm

-

Metso RKW353XZ - Automation Component

-

Metso PIC-09-50-200 - Automation Component

-

Metso LK-2027 - Linkage Kit

-

Metso XZB10025-011T12 - Moog Valve 9650962700

-

Metso XZB10025-010T12 - Moog Valve 9650965300

-

Metso-SP Transmitter Cable - Operating Unit with 10m Cable

-

Harkila Metso Hybrid - Hunting Jacket Willow Green

-

Metso ND8221/S1 - Neles Valve Positioner

-

Metso METSO10119 - ScreenCheck Component

-

Metso LK-2025 - Linkage Kit

-

Metso A416733 - IQweight External Air Gap Temperature Sensor

-

Metso RKC22MT - Automation Component

-

Metso A413281 - Automation Board

-

Metso LCP9HLY - Stainless Steel Enclosure

-

Metso NP704S/B1S1 - Pneumatic Positioner with I/P Converter

-

Metso BAH3 - Slurry Seal Type

-

Metso A413531-03 - PLC Module Chassis Rack

-

Metso P4610004 - MCAI Communicator Controller

-

Metso QN2AN03HDM - Quartz Valve Positioner Stonel

-

Metso RKW-352-XZ - Automation Component

-

Metso A4300081 - Kajaani LCD Display

-

Metso A428026 7B - Kajaani Rectifier Unit 1

-

Metso 202218 - Kajaani Sensor Power Supply SR 902660

-

Metso 9150 316SS CSTL - Jamesbury 150-2" BN50 Valve

-

Metso 81806 - IOP101 Module

-

Metso STOM000272 - Paper Bushing CR38

-

Metso 1975413 - Chain Hoist Links

-

Metso IMO G053-191597 - Minor Seal Kit

-

Metso VAL0087418 - Cylinder Valmet NTS6LV

-

Metso A413061 - DMU Board VPA 420355-4B

-

Metso P2620-80/25-100 - Automation Component

-

Metso VAL0035292 - Automation Component

-

Metso A413721 - Automation Component

-

Metso ST600 - Automation Component

-

Metso P4500001 - Automation Component

-

Metso SDBX/RA2 - CAT x KVM Extender

-

Metso D201126-DI8 - Digital Input Module

-

Metso D201189L - AI8H Analog Module

-

Metso NA004418 LK1016 - Wafersphere Actuator Mounting Bracket

-

Metso RKN172MTT - Repair Kit

-

Metso MM0311584 - Air Filter Kit RadialSeal

-

Metso 181517 - IOP301 Isolated Analog Input Module

-

Metso RAU3906506 - Automation Component

-

Metso 181208 - IOP332 Digital Input Module

-

Metso A413760 - AIF2C PCB Module

-

Metso 006 1089 36 - Shaft Bearing Seal

-

Metso A413046 - Automation Component

-

Metso VKJ650 - Automation Brake Component

-

Metso LK-1875 - Linkage Kit

-

Metso D201193L - FI4S24 Frequency Input Module

-

Metso D200533 - BIU82 Binary Input Module

-

Metso 500838-M1 - Impeller Pump Release Collar Assembly

-

Metso 2.00SB2ALUS19A - Pneumatic Cylinder 1.375 Stroke

-

Metso D201351 - RES Reserve Module

-

Metso A416100 - IQMoisture Spare Part Kit Halogen Lamp

-

Metso Slurry Pump - Back Liner

-

Metso 7088010042 - Bronze Lantern Ring

KONG JIANG

Add: Jimei North Road, Jimei District, Xiamen, Fujian, China

Tell:+86-15305925923