K-WANG

TEKTRONIX 5A22N Differential Amplifier

Core features:

Bandwidth: Maximum DC to 1MHz, bandwidth can be limited by HF-3dB (high frequency) and LF-3dB (low frequency) switches to improve signal-to-noise ratio;

Deflection coefficient: The knob skirt edge emits light and displays, supporting automatic scaling of 10X encoding probes;

Other: High common mode rejection ratio (CMRR), variable DC offset, suitable for displaying small signals at large DC levels.

TEKTRONIX 5A22N Differential Amplifier

Operation Instructions (Section 1)

1. Instrument description

Positioning: High gain differential amplifier plug-in unit, used for 5100 series oscilloscopes, can directly couple input to achieve high sensitivity.

Core features:

Bandwidth: Maximum DC to 1MHz, bandwidth can be limited by HF-3dB (high frequency) and LF-3dB (low frequency) switches to improve signal-to-noise ratio;

Deflection coefficient: The knob skirt edge emits light and displays, supporting automatic scaling of 10X encoding probes;

Other: High common mode rejection ratio (CMRR), variable DC offset, suitable for displaying small signals at large DC levels.

2. Panel controls and interfaces (key functions)

Control/Interface Function Description

Display switch plugin working status (only valid for vertical cabin), when turned on, the knob skirt light is on

POSITION adjusts the trajectory position on the screen

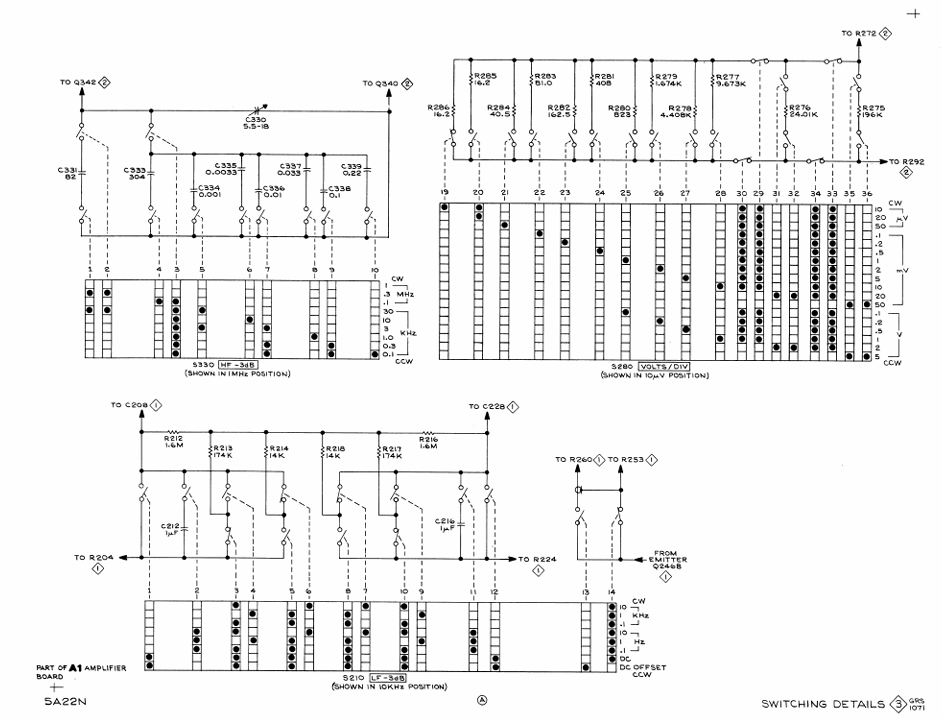

HF -3dB/LF -3dB - HF -3dB: 1-3-10 sequence with 7 levels (0.1kHz-1MHz), reducing the upper bandwidth limit and improving signal-to-noise ratio

-LF-3dB: 1-10-100 sequence with 7 levels (DC-10kHz), limited to 2Hz during AC coupling; adjustable DC offset in DC OFFSET level

VOLTS/DIV - Calibration mode: 18 levels 1-2-5 sequence, 10 μ V/Div to 5V/Div (accuracy 2%)

-Variable gear: Non calibrated continuous adjustment, range extended to 12.5V/Div

DC OFFSET (COARSE/FINE) requires LF-3dB to be placed in the DC OFFSET mode to achieve display adjustment of small signals at large DC levels

STEP ATTEN DC BAL balanced input amplifier to reduce trajectory offset during VOLTS/DIV switching

Input coupling button (AC/DC/GND/PRE CHG) - AC: capacitive coupling (blocking DC); DC: direct coupling

-GND: Input ground (disconnect signal); PRE CHG: Press AC+GND to pre charge the coupling capacitor to the signal DC level

+/-Input interface BNC interface,+positive signal deflects upwards, - positive signal deflects downwards; Equipped with a 10X encoded probe ring

3. Basic operation steps

Installation and startup:

Insertion: Align the plug-in guide rail with the 5100 series module compartment (priority vertical compartment: center/left; X-Y operation can be inserted into the horizontal compartment), and the panel should be level with the oscilloscope;

Power on: Adjust the oscilloscope brightness to the lowest level → Power on → Preset time base (2ms/Div) and trigger (automatic trigger).

Initial setup:

Set PLAY to ON,+/- input coupling to DC+GND, POSITION and STEP ATTEN BAL to median, HF/LF-3dB to full bandwidth, VOLTS/DIV to 50mV/Div, and variable gear to CAL (clockwise to bottom).

Preheating and trajectory adjustment:

Preheating: Short term DC measurement for 5 minutes, long-term DC measurement for 15 minutes;

Adjust the brightness to normal, and the trajectory should be near the center of the scale. Use POSITION to move the trajectory to 2 grids below the centerline.

Example of signal measurement:

Single ended DC coupling:+input connected to 400mV peak to peak calibration signal → release+GND → display 4 grid square waves (bottom alignment step 3 reference line);

Single ended AC coupling: POSITION moves the trajectory from bottom to center → presses AC → the trajectory shifts downward by about 2 grids (to the average value);

Differential AC coupling:+/- input connected to dual input cable → - input set to AC → display straight line (common mode signal suppressed).

4. Key precautions

Input protection: The maximum voltage of the input FET gate is ± 12V (diode clamp), and the input fuse will melt when the signal source current exceeds 1/16A;

Pre charge (PRE CHG): When measuring AC signals containing DC components, first connect the AC+GND signal → wait for 1 second for charging → release GND to avoid damaging the signal source due to coupling capacitor charging current;

High impedance input: When VOLTS/DIV is in the 50mV-10 μ V range, removing the circuit board jumper can disconnect the 1M Ω ground resistor, achieving high impedance input (requiring the signal source to provide a DC path for FET gate current).

5. Electrical characteristics (core parameters)

Specific parameters of characteristics

Bandwidth (-3dB) - DC coupling: DC to ≥ 1MHz (independent of deflection coefficient)

-AC coupling: 2Hz to ≥ 1MHz

Common mode rejection ratio (CMRR) - DC coupling: 10 μ V/Div-0.1mV/Div range ≥ 100dB (DC-30kHz, 20Vp-p sine wave); 0.1V/Div-5V/Div mode ≥ 50dB (100Vp-p sine wave)

-AC coupling: ≥ 80dB at 5kHz and above, reduced to 50dB at 10Hz

DC offset range -10 μ V/Div-50mV/Div range: ± 0.5V

-100mV/Div-5V/Div mode: ± 50V

Input RC 1M Ω (± 0.1%) in parallel at approximately 47pF

Maximum input voltage DC coupling: 10V (DC+peak AC) (10 μ V-50mV range); 350V (DC+peak AC) (100mV-5V range)

-AC coupling: 350VDC+10V peak AC (10 μ V-50mV range, pre charged); 350V (DC+peak AC) (100mV-5V range)

Noise at full bandwidth (DC-1MHz) ≤ 20 μ V (25 Ω source resistance, tangent measurement)

Working principle (Section 2)

1. Overall block diagram path

Signal → Input coupling (AC/DC/GND) → Input attenuator (1X/100X, frequency compensation) → Pre amplifier (differential structure, floating ground power supply) → Low frequency limiting circuit (LF-3dB switching) → Gain switching stage (VOLTS/DIV control) → Offset generator (DC OFFSET) → Isolation stage (emitter follower) → Output amplifier (push-pull structure, POSITION adjustment) → Trigger signal amplifier (output to time base plugin, 0.25V/display panel).

2. Analysis of core circuit modules

Input attenuator:

Attenuation ratio: VOLTS/DIV 0.1V-5V range with 100X attenuation, 10 μ V-50mV range with 1X attenuation;

Features: Frequency compensation, maintaining 1M Ω//47pF input characteristics, balancing common mode signals through R132 (Atten DC CMR).

Pre amplifier:

Structure: Two identical operational amplifiers form a differential circuit (Q150A/B, Q190A/B, Q200A/B);

Floating power supply: composed of Q170/Q176 (constant current source) and VR173/175/176 (Zener transistor), it maintains the stability of the amplification device operating point and improves CMRR as the common mode signal changes;

Gate current compensation: Regulate R121/R127 to offset FET gate leakage current (≤ 100pA) and avoid high-sensitivity offset (such as 100pA × 1M Ω=100 μ V offset in 10 μ V/Div mode, which may cause trajectory offset screen).

DC offset generator:

Structure: Q240/Q244/Q246A/B form a voltage comparator, with VR251 (transistor) providing a reference voltage;

Function: By adjusting COARSE (R260) and FINE (R268), offset current is generated to cancel the DC component of the input signal, with a maximum cancellation of 0.5V.

Output amplifier:

Structure: Push pull amplifiers Q348/Q352, R351 (GAIN) adjust the total gain to match the requirements of the host;

Position adjustment: Q360/Q362 (positioning current drive), R360 (POSITION) changes the current to adjust the static position of the CRT beam.

Calibration (Section 3)

1. Calibration prerequisites and preparations

Applicable scenarios: After instrument maintenance, long-term use (component aging) leads to accuracy deviation;

Environmental requirements: Temperature of 20-30 ℃, preheating for 20 minutes;

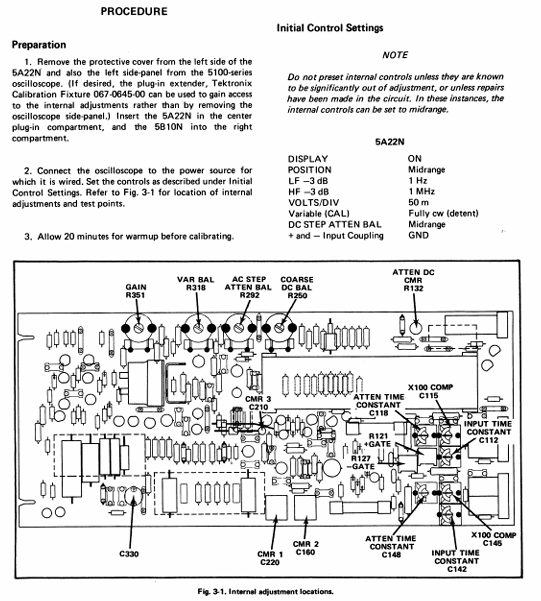

Equipment disassembly: Remove the left protective cover of 5A22N and the left panel of 5100 series oscilloscope (or use plug-in extender 067-0645-00);

Initial settings: Set the 5A22N control to POSITION median LF-3dB=1Hz、HF-3dB=1MHz、VOLTS/DIV=50mV、 Variable gear=CAL,+/- input=DC+GND, STEP ATTEN BAL median; The 5B10N time base is set to automatic triggering,+slope, and AC coupling.

2. Required testing equipment (including accessories)

Specific requirements/model examples for equipment types

Oscilloscope System 5100 Series (including 5B10N Time Base Plugin)

Constant amplitude sine wave generator frequency 2Hz-1MHz, output 0.5V-40Vp-p (such as General Radio 1310-B)

Standard amplitude calibrator 1kHz square wave, output 5mV-50V, accuracy ± 0.25% (recommended 067-0502-01)

Accessories - Coaxial Line: 50 Ω, 42 inches, BNC(012-0057-01)

-Dual input cable: matching signal path, BNC(067-0525-00)

-1000:1 voltage divider: accuracy ± 0.2% (067-0529-00)

-Input RC Normalizer: 1M Ω× 47pF (067-0541-00)

-Serial terminal: 50 Ω, accuracy ± 2% (011-0049-01)

3. Key Calibration Steps (Core 8 Steps)

Step attenuator balance:

R292 (AC STEP ATTEN BAL): Switch between VOLTS/DIV 50mV-0.1V to minimize trajectory offset;

Adjust R318 (VAR BAL): Shift the variable gear from CLOCKWISE to COUNTERCLOCKWISE to minimize trajectory deviation;

Adjust R250 (COARSE DC BAL): Set LF-3dB to DC, switch VOLTS/DIV 50mV-0.1V, and minimize trajectory offset.

Gate current regulation:

+Input to 50 Ω terminal → LF-3dB=DC → Release+GND → Switch+AC, adjust R121 (+GATE CURRENT), minimize trajectory offset;

-Input to 50 Ω terminal → press+GND → release - GND → switch - AC, adjust R127 (- GATE CURRENT), minimize trajectory deviation.

Attenuator DC common mode rejection:

Release+/- GND → VOLTS/DIV=0.1V →+/- Input through dual cables connected to a 50V square wave (calibrator) → Adjust R132 (ATT DC CMR) to display the minimum amplitude.

Input compensation:

-GND pressed ->VOLTS/DIV=50mV ->+input connected to 0.5V square wave (normalized by RC) ->C118 adjusted (Atten Time Constant), with the best square wave front;

Similarly, input C148, C145, C142.

Amplifier gain calibration:

VOLTS/DIV=10mV →+input connected to 50mV square wave → adjust R351 (GAIN), display amplitude exactly 5 grids;

Turn the variable gear to COUNTERCLOCKWISE, with a display amplitude of<2 grids, and then turn it back to CAL.

VOLTS/DIV accuracy check:

VOLTS/DIV=5V →+input connected to 20V square wave (through 1000:1 voltage divider X1 gear) → gradually decrease VOLTS/DIV, synchronously adjust the calibrator output, ensure display of 4-5 grids, accuracy ± 2%;

VOLTS/DIV=5mV gear → voltage divider set X1000 → calibrator output 20V → HF-3dB=10kHz → repeat the above checks.

Common mode rejection ratio (CMRR) calibration:

Release - GND → VOLTS/DIV=10mV →+/- input connected to 20Vp-p, 50kHz sine wave → adjust C160 (CMR 2), display minimum;

VOLTS/DIV=50 μ V → Time base=10 μ s/Div → Adjust C220 (CMR 1), display minimum;

LF-3dB=0.1kHz → switch to C210 (CMR 3), display minimum, repeat until there is no interaction effect.

Bandwidth calibration:

-GND pressed → VOLTS/DIV=1mV → LF-3dB=DC → Time base=1ms/Div →+input connected to 1kHz, 8-grid sine wave → Generator output 1MHz → C330 adjusted, display amplitude reduced to 5.6 grid (-3dB point).

Drawings and Parts List (Section 4)

1. Symbols and reference identification rules

Component symbol: Following ANSI Y32.2-1970 standard, logical symbol follows MIL-STD-806B (positive logic);

Reference identification prefixes: C=capacitor, R=resistor, Q=transistor, CR=diode, F=fuse, J=fixed connector, S=switch, VR=voltage regulator (transistor), etc.

2. Core Parts List (Example)

Part Type Reference Identification Tektronix Part Number Specification Description

Capacitor C103 283-0002-00 0.01pF, ceramic, 500V

Capacitor C133 283-0626-00 1800pF, mica, 5%

Resistance R120 322-0481-07 1M Ω, 1/4W, 1/10%

Resistance R121 311-1223-00 250 Ω, variable

Transistors Q150A/B 151-1027-00 silicon FET, replaceable with D/2N4394 or FD1392

Transistors Q103/Q105 151-0347-00 silicon NPN, replaceable with 2N5551

Diode VR138 152-0520-00 Zener diode, 1W, 12V, replaceable with UZ8712 or HW12B

Switch A10 (LF-3dB) 105-0310-00 cam switch

Switch S280 (VOLTS/DIV) 105-0309-00 cam switch

Circuit board A1 670-1894-00 main circuit board component

- YOKOGAWA

- Reliance

- ADVANCED

- SEW

- ProSoft

- WATLOW

- Kongsberg

- FANUC

- VSD

- DCS

- PLC

- man-machine

- Covid-19

- Energy and Gender

- Energy Access

- Renewable Integration

- Energy Subsidies

- Energy and Water

- Net zero emission

- Energy Security

- Critical Minerals

- A-B

- petroleum

- Mine scale

- Sewage treatment

- cement

- architecture

- Industrial information

- New energy

- Automobile market

- electricity

- Construction site

- HIMA

- ABB

- Rockwell

- Schneider Modicon

- Siemens

- xYCOM

- Yaskawa

- Woodward

- BOSCH Rexroth

- MOOG

- General Electric

- American NI

- Rolls-Royce

- CTI

- Honeywell

- EMERSON

- MAN

- GE

- TRICONEX

- Control Wave

- ALSTOM

- AMAT

- STUDER

- KONGSBERG

- MOTOROLA

- DANAHER MOTION

- Bentley

- Galil

- EATON

- MOLEX

- Triconex

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- KOLLMORGEN

- Beijer

- Endress+Hauser

- schneider

- Foxboro

- KB

- REXROTH

- YAMAHA

- Johnson

- Westinghouse

- WAGO

- TOSHIBA

- TEKTRONIX

- BENDER

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- XP POWER

- Baldor

- Meggitt

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- IBA

-

ABB PFSA240 Roll DC Supply Unit 3BSE073476R1 Industrial Stressometer Power Supply Module for Rolling Mill Systems

-

ABB PFSA107-Z42 DTU Stressometer Digital Transmission Unit High Precision Strip Tension Measurement Module

-

GE AT868-2-1-1 Ultrasonic Flow Transmitter AquaTrans AT868 Dual Channel Industrial Flow Meter

-

ABB SCC-C 23070-0-10232110 Industrial Control Module Automation System Communication Controller

-

APPLIED MATERIALS 0041-96185 - Heater Assy with 0150-45776 0190-60492 AMAT

-

APPLIED MATERIALS 0021-33426 - SHIELD INNER SINGLE 300MM NO COIL AMAT

-

APPLIED MATERIALS 0140-01905 - HARNESS ASSY DUAL IHC PRESS CONT ADAPTER 16798 AMAT

-

APPLIED MATERIALS 0051-01848 - LINE VAC EXHAUST CH Y LEAK CHECK PORT EPI AMAT

-

APPLIED MATERIALS 0010-02863 - P5000 150mm Teos Susceptor AMAT

-

APPLIED MATERIALS 0010-14056 - ASSY INJECT NOZZLE STANDARD AMAT

-

APPLIED MATERIALS 0020-34694 - LINER GDP R2 OXIDEGECO AMAT

-

APPLIED MATERIALS 0195-07416 - SYCAMORE-X CMP POLISHER I/O ASSEMBLY AMAT

-

APPLIED MATERIALS 0200-09036 - WAFER LIFT PIN AMAT

-

APPLIED MATERIALS 0021-39090 - FLANGE 10" CONFLAT ADAPTOR AMAT

-

APPLIED MATERIALS 0100-99011 - GAS INTERLOCK AMAT

-

APPLIED MATERIALS 0100-11002 - digital I/O card AMAT

-

APPLIED MATERIALS 0190-40000 - PNEUMATIC MANIFOLD CHAMBER 32903 AMAT

-

APPLIED MATERIALS 0021-39792 - PERF PLATE OX. 200 MM TEOS 21896 AMAT

-

APPLIED MATERIALS 0040-04896 - BELL JAR QUARTZ Q-KOTE 200MM AMAT

-

APPLIED MATERIALS 0020-20653 - BASE HEATER AMAT

-

APPLIED MATERIALS 0190-75057 - Lift Cylinder Assy AMAT

-

APPLIED MATERIALS 0010-70345 - Applied Materials 0042-01927

-

APPLIED MATERIALS 0100-91024 - PWBA PRE-ACCEL VENDOR I/F PCB 9500 IMPLANT AMAT

-

APPLIED MATERIALS 0041-56144 - HEATER PEDESTAL ASSEMBLY ENP FCVD EDGE AMAT

-

APPLIED MATERIALS 0090-00836 - SOURCE MOTOR ASSY 0040-24074 GFB5G10 FBLM5120W AMAT

-

MKS 0190-63631 - MASS FLOW VERIFIER MFVA-33168 AMAT

-

APPLIED MATERIALS 0100-35070 - ASSY PCB RF GENERATOR INTERFACE AMAT

-

APPLIED MATERIALS 0010-32221 - ASSEMBLY ROUGH THROTTLE VALVE DRIVE 300MM AMAT

-

SANYO DENKI 0190-14713 - P30B06040HXS8RM AC SERVO MOTOR BL SUPER AMAT

-

APPLIED MATERIALS 0190-14224 - FLEX DIST PANEL AMAT

-

APPLIED MATERIALS 0190-23897 - SPECIFICATION EXMP SYNCNET STAND ALON 14535 AMAT

-

APPLIED MATERIALS 0010-04542 - HEATER ASSY 200MM FC WXZPLUS OSCR 15607 AMAT

-

APPLIED MATERIALS 0190-51414 - AC SERVO DRIVER SGDV-OCA05AY890AA AMAT

-

APPLIED MATERIALS 0020-31747 - P5000 LOADLOCK LID WAFER TXR CHMBR 0020-32930 12573 AMAT

-

APPLIED MATERIALS 0620-01727 - CABLE ASSY SIGNAL RBN 50PIN DSUB EMI RES 17781 AMAT

-

APPLIED MATERIALS 0190-A9510 - IP POWER SUPPLY 33361 AMAT

-

APPLIED MATERIALS T1101-05-000-30 - CRYO TIGER COMPRESSOR AMAT

-

APPLIED MATERIALS 0040-13338 - LINK 1 UPPER 7.2 DEGREE OFFSET CR 300MM 38177 AMAT

-

APPLIED MATERIALS 0190-06926 - Cable SQS R/A TO SQS R/A #2 AMAT

-

APPLIED MATERIALS 0200-00705 - EDGE RING THIN 200MM AMAT

-

APPLIED MATERIALS 0190-01399 - INLINE O3 SNSR ULTRA FULL FLOW HI-CON 6627 AMAT

-

APPLIED MATERIALS 0190-21054 - RF MATCH CABLE ASSEMBLY PRECLEAN 2 AMAT

-

APPLIED MATERIALS 0041-12156 - REFLECTOR PLATE INJECT 300MM RADIANCE PLUS 29763 AMAT

-

MKS 0100-03680 - PCB CHMBR DIST 0090-09483 AS00363-16 35465 AMAT

-

APPLIED MATERIALS E11355460 - Plasma Detector E11355470 Rev.B AMAT

-

APPLIED MATERIALS 0021-33981 - LOWER SHIELD AMAT

-

APPLIED MATERIALS 0100-00583 - GAS PANEL CONTROLLER DIST AMAT

-

APPLIED MATERIALS 0010-54820 - IPC VALVE ASSEMBLY FM 1/2" INTER-PLATEN SPRAY AMAT

-

APPLIED MATERIALS 0020-31747 - P5000 LOADLOCK LID WAFER TXR CHMBR 0020-32930 12573 AMAT

-

APPLIED MATERIALS 0020-40566 - BLANK-OFF POSITION E-F ENP AMAT

-

APPLIED MATERIALS 0021-31023 - Flange Spacer Automatch Single RPS Producer SE AMAT

-

APPLIED MATERIALS 0020-21225 - WEIGHT RING 300MM TITAN PROFILER AMAT

-

APPLIED MATERIALS 0190-A9510 - IP POWER SUPPLY 33361 AMAT

-

APPLIED MATERIALS 0100-90618 - PCB H1 GROUND PDU MOTHER BOARD 0100-90036 AMAT

-

APPLIED MATERIALS 0010-04542 - HEATER ASSY 200MM FC WXZPLUS OSCR 15607 AMAT

-

APPLIED MATERIALS 0020-31658 - CLAMP VESPEL OX-MLR-NIT 200MM AMAT

-

APPLIED MATERIALS 0021-09974 - WINDOW SAPPHIRE PUMPING PLATE AMAT

-

APPLIED MATERIALS 0051-01849 - LINE VAC EXHAUST ELBOW CH Y FAC TRAY EPI 30 AMAT

-

APPLIED MATERIALS 0010-29842 - 300mm DBR High Temp Belt Wrist Titanium AMAT

-

APPLIED MATERIALS 1410-01166 - Heating Jacket AMAT

-

APPLIED MATERIALS 0620-01727 - CABLE ASSY SIGNAL RBN 50PIN DSUB EMI RES 17781 AMAT

-

APPLIED MATERIALS 0010-70345 - Applied Materials 0042-01927

-

APPLIED MATERIALS 0090-00836 - SOURCE MOTOR ASSY 0040-24074 GFB5G10 FBLM5120W AMAT

-

APPLIED MATERIALS 0190-46837 - INFRARED THERMOMETER COMM BOX RAYMI3COMM 30009 AMAT

-

APPLIED MATERIALS 0020-31886 - FLANGE INSULATION UNIBODY .400 THK AMAT

-

APPLIED MATERIALS 0010-05920 - CONTROLLER CCM PROD ETCH CS-PM CARD CAGE AMAT

-

APPLIED MATERIALS 0242-30292 - KIT 20 SCCM MFC W/HRDWR UNIBODY 6449 AMAT

-

APPLIED MATERIALS 0040-41061 - JIG FOUR PT LEVELING TOOL TXZ 300MM AMAT

-

APPLIED MATERIALS 0020-30287 - ADAPTER RING PUMPING PLATE 200MM COMMO AMAT

-

APPLIED MATERIALS 0041-12156 - REFLECTOR PLATE INJECT 300MM RADIANCE PLUS 29763 AMAT

-

APPLIED MATERIALS 0010-37866W - ASSY INT ISRM MODULE FULL SCAN SMG AMAT

-

APPLIED MATERIALS 0090-08137 - 300MM TXZ DLI HEATER CONTROLLER MODULE AMAT

-

APPLIED MATERIALS 0040-20006 - ARM WELDMENT SOURCE STD 8464 AMAT

-

APPLIED MATERIALS 0090-07392 - Dual RF filter AMAT

-

APPLIED MATERIALS 0190-06926 - Cable SQS R/A TO SQS R/A #2 AMAT

-

APPLIED MATERIALS 0020-70279 - LIFTER 150MM WAFER ORIENTER P5000 AMAT

-

APPLIED MATERIALS 0190-35652 - SERIPLEX MUX I/O PCB AMAT

-

APPLIED MATERIALS 0100-11002 - digital I/O card AMAT

-

APPLIED MATERIALS E11355460 - Plasma Detector E11355470 Rev.B AMAT

-

APPLIED MATERIALS 0010-19188 - ASSY COOLDOWN LIFT 34703 AMAT

-

APPLIED MATERIALS 0100-00975 - PCB STEPPER CONTROLLER 2 8099 AMAT

-

APPLIED MATERIALS 0190-16236 - MOTOR ENCODER ASSY ROBOT WRIST MIRRA CMP AMAT

-

APPLIED MATERIALS 0040-48671 - LEFT GUIDE 300MM L-DOOR 37961 AMAT

-

MKS 0100-03680 - PCB CHMBR DIST 0090-09483 AS00363-16 35465 AMAT

-

APPLIED MATERIALS 0190-01399 - INLINE O3 SNSR ULTRA FULL FLOW HI-CON 6627 AMAT

-

APPLIED MATERIALS 8330 - Pair Of Side viewport Panels AMAT

-

APPLIED MATERIALS 0190-75057 - Lift Cylinder Assy AMAT

-

APPLIED MATERIALS 0100-02016 - PCB ASSY ANALOG SYNC DETECT 904-125N AMAT

-

Abaco Systems 0090-08517 - VMICPCI-7326 PCB 38085 AMAT

-

APPLIED MATERIALS 0100-20069 - ASSY WAFER ORIENTER BOARD 0100-02797 AMAT

-

ELEKTRO-AUTOMATIK EA-PS 9036-070 - S01 POWER SUPPLY 625-795365 AMAT

-

APPLIED MATERIALS 3310-00139 - CAPACITANCE PIRANI GAUGE C-SEAL MOUNT 15-PIN AMAT

-

APPLIED MATERIALS 0010-00510 - ASSY BEARING STD 36806 AMAT

-

APPLIED MATERIALS 0041-13895 - FACEPLATE 26MIL CENTERHOLE RF CAP 300MM SACVD 13964 AMAT

-

APPLIED MATERIALS T1101-05-000-30 - CRYO TIGER COMPRESSOR AMAT

-

APPLIED MATERIALS 0050-10076 - WELDMENT DUAL HE MANF SACVD 20243 AMAT

-

MKS 0190-48179 - AS01294-05237-030 Hardened DeviceNet I/O Block AMAT

-

APPLIED MATERIALS 0240-75102 - 8" Transfer Blade 200mm End Effector AMAT

-

APPLIED MATERIALS 0110-90770 - Index Control PCB AMAT

-

APPLIED MATERIALS 0090-91209 - SOURCE SUPPRESSION CLAMPING BOX AMAT

-

APPLIED MATERIALS 0200-01427 - ISOLATOR CERAMIC CVD LOW K 300MM PROD AMAT

-

APPLIED MATERIALS 0021-03637 - FACEPLATE SILANE PRODUCER 200MM AMAT

-

APPLIED MATERIALS 0010-09837 - Wafer Lift Tungsten Precision 5000 AMAT

-

APPLIED MATERIALS 0101-57014 - PCB DEFLECTION-AMPLIFIER BOARD D-AMP 50-06 26296 AMAT

-

APPLIED MATERIALS 0190-36715 - PCB GP IO DISTRIBUTION AMAT

-

APPLIED MATERIALS 0660-00078 - PCB ASSY DNET ANALOG I/O CDN396 DIP-506-068 13392 AMAT

-

APPLIED MATERIALS 0190-B4670 - FIBER HARNESS DVD2-SBBI AMAT

-

APPLIED MATERIALS 1080-02356 - ACCELNET SINGLE AXIS SERVO DRIVE 800-2122 AMAT

-

APPLIED MATERIALS 0040-02937 - WATER MANIFOLD TXZ CIP 200 & 300MM AMAT

-

APPLIED MATERIALS 0040-08944 - LID ANNEAL ECP 200MM AMAT

-

SMC INOI-7134-111 - 4-PORT DEVICENET UPA MODULE Pressure Control AMAT

-

SMC INOI-7134-21 - 4-PORT DEVICENET UPA MODULE Pressure Control AMAT

-

APPLIED MATERIALS 0100-40024 - ASSY WPCBA LOADLOCK INTERCONNECT BOARD AMAT

-

APPLIED MATERIALS 0660-01635 - Chamber P2 Board A AMAT

-

APPLIED MATERIALS 0041-31945 - DOOR ENP ALUM SPD SLIT VALVE VITON LLK 3 AMAT

-

APPLIED MATERIALS 0040-48671 - LEFT GUIDE 300MM L-DOOR 37961 AMAT

-

APPLIED MATERIALS 0051-01849 - LINE VAC EXHAUST ELBOW CH Y FAC TRAY EPI 30 AMAT

-

APPLIED MATERIALS 0040-81661 - CATHODE FACILITY PLATE 35320 AMAT

-

APPLIED MATERIALS 0040-20006 - ARM WELDMENT SOURCE STD 8464 AMAT

-

APPLIED MATERIALS 0110-90770 - Index Control PCB AMAT

-

APPLIED MATERIALS 8330 - Pair Of Side viewport Panels AMAT

-

APPLIED MATERIALS 0040-81155 - LINER LOWER AMAT

-

APPLIED MATERIALS 0100-90618 - PCB H1 GROUND PDU MOTHER BOARD 0100-90036 AMAT

-

APPLIED MATERIALS 0040-47677 - FACEPLATE SIN XG DXZ DCVD AMAT

-

APPLIED MATERIALS 0020-31658 - CLAMP VESPEL OX-MLR-NIT 200MM AMAT

-

CTI-CRYOGENICS 0190-54040 - ON-BOARD IS CONTROLLER 34633 AMAT

-

APPLIED MATERIALS 0020-21665 - SHIELD AL/TI 8 INCH WAFER AMAT

-

APPLIED MATERIALS 0090-10397 - RF FILTER BOX AMAT

K-JIANG

Add: Jimei North Road, Jimei District, Xiamen, Fujian, China

Tell:+86-15305925923