K-WANG

Saia PCD4.U100 System Migration Complete Guide

However, a comprehensive replacement of the control system often means high costs and long downtime. Saia Burgess Controls (SBC) has launched the PCD4.U100 migration kit to address this pain point. This innovative solution allows users to upgrade the core processing unit to a more powerful PCD2.M5xxx or PCD3.Mxxxx series CPU while retaining the original PCD4 I/O module. This article will provide you with a detailed analysis of the hardware installation, address mode configuration, software migration process, and professional technical details of the PCD4.U100 suite based on official technical documents, and offer you a comprehensive operation guide.

Saia PCD4.U100 System Migration Complete Guide

Introduction: The inevitable choice for upgrading industrial control systems

In the field of industrial automation, lifecycle management of control systems has always been a core challenge faced by engineers. With the rapid iteration of technology, although the early Saia PCD4 series PLCs (programmable logic controllers) had excellent performance at the beginning of their design, their processing speed, memory capacity, and communication capabilities have gradually become limited in modern high demand application scenarios. In order to ensure the continuity of the production line and utilize the latest technological dividends, system upgrades have become inevitable.

However, a comprehensive replacement of the control system often means high costs and long downtime. Saia Burgess Controls (SBC) has launched the PCD4.U100 migration kit to address this pain point. This innovative solution allows users to upgrade the core processing unit to a more powerful PCD2.M5xxx or PCD3.Mxxxx series CPU while retaining the original PCD4 I/O module. This article will provide you with a detailed analysis of the hardware installation, address mode configuration, software migration process, and professional technical details of the PCD4.U100 suite based on official technical documents, and offer you a comprehensive operation guide.

Hardware migration architecture and compatibility review

A comprehensive review of the hardware compatibility of the existing system is the cornerstone of a successful migration before embarking on any physical operations. The core logic of the PCD4.U100 kit is to act as a "bridge" connecting the old PCD4 backplane bus with the new PCD2/PCD3 CPU bus.

1.1 Core Components and Connection Logic

The first step in migration work is the replacement of physical hardware. According to the official migration checklist, the standard operating procedure is as follows:

Remove old CPU: After power off, remove the old PCD4 CPU from the PCD4 rack. At this point, the PCD4. N2x0 power module must be retained on the rack as it serves as the foundation for system power supply.

Install PCD4.U100: Insert the PCD4.U100 module into the slot where the original CPU is located. This module serves as a bus converter.

Connect the new CPU: Use a dedicated connection cable to connect the PCD4.U100 to the new CPU.

If using a PCD2.M5xxx CPU, it is necessary to use a PCD2.K106 cable.

If using a PCD3.Mxxxx CPU, a PCD3.K116 or PCD3.K106 cable is required.

1.2 Key Compatibility Limitations

Not all old hardware can seamlessly support this upgrade, ignoring the following details may result in hardware damage or system failure:

Power module version: If a PCD4. N2x0 power module is used in the system, its hardware version must be Version B or a later version. The document clearly states that using older versions of power modules may cause irreversible physical damage to the PCD4.U100 module. This is because the new CPU has stricter requirements for power stability and startup timing.

CPU firmware requirements: The new PCD2.M5xxx or PCD3.Mxxxx CPU must be equipped with the NT-OS operating system, and the minimum firmware version requirement is 1.10.16. The old version of the operating system cannot recognize the bus mapping logic of PCD4.U100.

Unsupported modules: Not all I/O modules in the PCD4 series can be recognized by the new system. Especially the PCD4. HXxx series modules (usually specific high-voltage or special function modules) are not supported in this upgrade and must be removed or alternative solutions sought in the migration plan.

Serial interface: The original serial port of the PCD4 CPU will no longer be available, and the system will rely on the onboard serial interface of the new CPU (PCD2. M5 or PCD3) for communication.

Deep analysis of I/O address mode

The most complex and critical part of the PCD4.U100 kit is the configuration of the address mode. Due to the differences in the I/O addressing architecture between PCD4 and PCD3/PCD2, address conflicts must be coordinated through physical switches and software settings. There is a multi position switch on the back of the module for setting the starting address of the PCD4 I/O module.

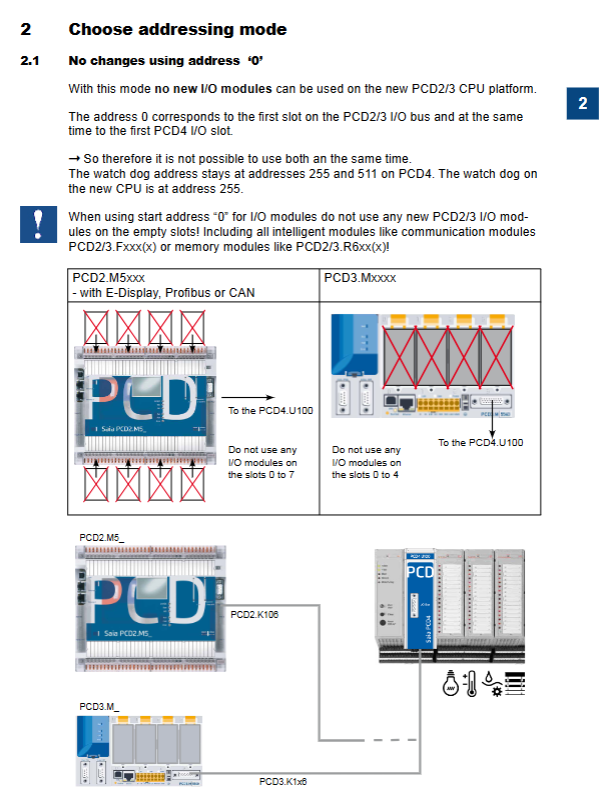

2.1 Mode 1: Starting Address' 0 '(No Change Mode)

This is the simplest configuration mode, suitable for scenarios where no new PCD2/3 I/O modules are intended to be added.

Switch position: Set the switch to Pos. 0 or Pos. 1.

Pos. 0: corresponds to situations where PCD2.M5xxx does not have an expansion module, or PCD3.Mxxxx has an expansion but no I/O module.

Pos. 1: Corresponding to the case of PCD3.M3xxx without expansion and no I/O module.

Address logic: The address of the PCD4 I/O module remains unchanged, starting from address 0.

Important limitation: In this mode, slot 0 of the new CPU (corresponding to slot 0-7 of PCD2.M5xxx and slot 0-4 of PCD3.Mxxxx) is logically occupied by PCD4 I/O. Therefore, it is strictly prohibited to insert new PCD2/3 I/O modules, including intelligent modules (such as communication module PCD2/3. Fxxx or memory module PCD2/3. R6xx), into these slots. If inserted, it will cause serious address conflicts.

Watchdog address: The watchdog of PCD4 is kept at addresses 255 and 511, while the watchdog of the new CPU is located at address 255. The system will maintain two watchdog instances.

2.2 Mode 2: Starting Address' 256 '(Extended Mode)

This mode provides the system with scalability, allowing users to utilize the new platform's scalability while retaining old I/O.

Switch position: Set the switch to Pos. 2 or Pos. 3.

Pos. 2: Suitable for PCD3.Mxxxx with expansion or PCD2.M5xxx without expansion, allowing up to 8 new PCD2/3 I/O modules to be used.

Pos. 3: Suitable for PCD3.Mxxxx without expansion, allowing up to 4 new PCD3 I/O modules to be used.

Address offset: All PCD4 I/O addresses will be offset backwards by 256 units as a whole. For example, the module originally with address 0 has now become 256.

Dual watchdog mechanism: In this architecture, the system will explicitly have two watchdog mechanisms. The watchdog of the new CPU is located at address 255, while the watchdog of the PCD4 system is mapped to addresses 511 and 767. Programmers must adapt to this change in the user program.

2.3 Address impact of serial communication

The address allocation for serial communication is also affected by the mode:

When using the onboard serial port of a new CPU and not using the PCD2/3 I/O module, the PCD4 I/O address range starts from 0.

When using PCD3. Fxxx or PCD2. Fxxx communication modules, these modules occupy the I/O address space, forcing the starting address of PCD4 I/O to automatically adjust to 256. This requires the user program to make corresponding code modifications.

Software environment upgrade and project migration

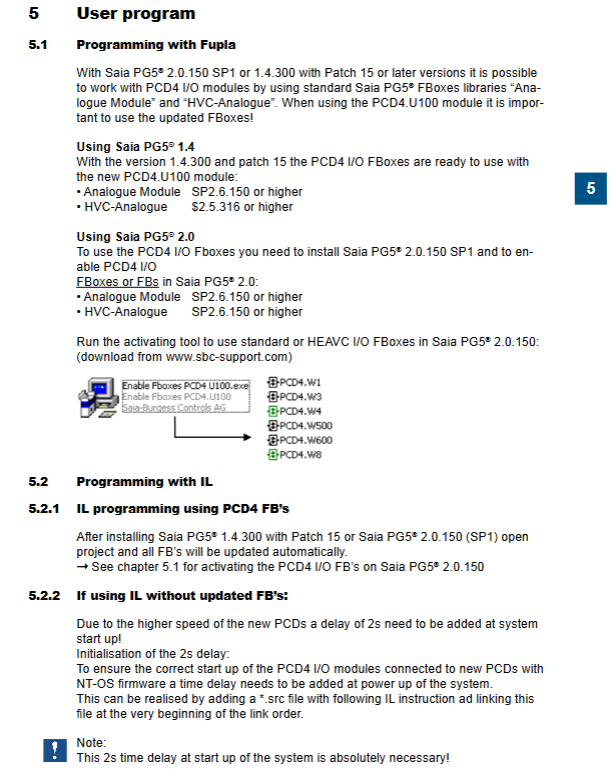

After the hardware connection is completed, the establishment of the software environment and project migration are the key to the system's "resurrection". Saia PG5 ® Control programming software is the core tool for this process.

3.1 Software version requirements

In order to support PCD4.U100 and the new CPU architecture, PG5 software must be updated to a specific version:

Saia PG5 ® 1.4.300: Patch 15 or higher must be installed.

Saia PG5 ® 2.0: SP1 (Service Pack 1) or higher must be installed.

3.2 Project Migration Steps

Backup: Before performing any operation, all old project files (PG3 or PG4 projects) must be fully backed up.

Project update: Open PG5 and import old projects. The software will automatically prompt to update the project structure.

Remove CPU specific features: Old projects may contain specific functional blocks or instructions for the PCD4 CPU that cannot be parsed in the new CPU and must be manually removed.

Hardware configuration: In the hardware configurator of PG5, change the CPU model to the actual new model used (PCD2.M5_ or PCD3. M0).

Activate FBox library: For PG5 2.0 users, the activation tool needs to be manually run to enable the FBox library for PCD4 I/O. This includes the "Analog Module" and the "HVC Analog" library. Only after activation can the software correctly recognize and control the I/O module of PCD4.

User program adaptation and IL code deep optimization

This is the most technologically advanced stage in the migration process. Due to the much higher running speed of the new CPU compared to the old PCD4, simple program porting often leads to timing errors or initialization failures. The manual provides a detailed list of adaptation schemes for instruction list (IL) programming.

4.1 The necessity of starting delay

Phenomenon: The startup speed of the new CPU is extremely fast, and it may start sending control instructions before the PCD4 I/O module completes its initialization, resulting in abnormal response of the I/O module.

Solution: A 2-second delay must be forcibly inserted at system startup.

Implementation method: Create a source file named Wait_2s.src and place it at the top of the link order. The code logic is as follows:

$INIT

ACC H

LD T 0

T#2s ; Set the delay time to 2 seconds

LOOP:

STH T 0

JR H LOOP

ACC H

$ENDINIT

Through this code, the program will loop and wait for timer T0 to reach 2 seconds during the initialization phase, ensuring that the modules on the PCD4 backplane have enough time to power on, reset, and be ready.

4.2 Timing correction of analog module (PCD4. W100)

PCD4.W100 is an analog module, and its A/D (analog-to-digital conversion) and D/A (digital to analog conversion) processes require specific physical time. On old CPUs, due to the longer instruction execution cycle, the program running speed naturally covers this delay. But on high-speed CPUs, continuous read and write instructions ignore the conversion time of modules.

Correction plan: Insert NOP (null operation) instruction between read and write operations.

Reading process: Select channel ->Start conversion ->Wait (STH I 15 detects high level) ->Read data. During this process, the insertion of NOP instructions prevents the CPU from polling status bits too quickly.

Writing process: Output data ->Select channel ->Start conversion ->Insert NOP. This ensures that the data is stably written into the module register before the next operation.

4.3 Initialization of Advanced Modules (PCD4. W500/W600)

For advanced modules such as PCD4.W500 and W600, simple delays are no longer sufficient to complete initialization and must be explicitly configured through specific functional blocks (CFB).

The control function block must be called in XOB 16 (initialization interrupt block):

Restart control: First, call CFB Control with parameter Restart warm (7) to perform a hot restart on the module.

Configuration download: Then call CFB config to write the configuration data block (DB) to the module.

If multiple W500 or W600 modules are used in the system, it is recommended to handle all restart instructions centrally, and then handle all configuration instructions centrally. This batch processing method can optimize initialization time and prevent system startup timeout.

System functional differences and exception handling

The upgraded system has subtle but significant differences in underlying logic compared to the old system, which engineers need to pay special attention to when debugging.

5.1 LED status indication

On the PCD4. N210 power/bus module, the functionality of some LED indicator lights has changed:

Effective LEDs:+24V,+5V (bus signal), Reset (restart signal), Watch Dog.

Failed LED: The battery indicator light, RUN/HALT operation indicator light, and CLEAR clear indicator light will no longer have their original functions after connecting to a new CPU. This is because these states are now directly managed by the indicator lights on the new CPU panel.

5.2 Exception Handling Block (XOB)

Abandonment of XOB 5: In the PCD4 system, XOB 5 is used to process/IOQUIT signals (I/O exit confirmation). The signal mechanism has been removed in the new CPU architecture, so the XOB 5 program block will no longer be executed. Suggest marking it as a comment when migrating code to avoid confusion.

The functional evolution of XOB 1: XOB 1 is used to detect I/O bus power failures. Combined with the PCD4. N210 power module, the detection capability of XOB 1 has been enhanced. It can not only detect+5V output, but also monitor+/-15V voltage and input voltage. The delay time for the system to detect the fault is about 500ms, which provides a basis for writing a fault safety program.

- YOKOGAWA

- Reliance

- ADVANCED

- SEW

- ProSoft

- WATLOW

- Kongsberg

- FANUC

- VSD

- DCS

- PLC

- man-machine

- Covid-19

- Energy and Gender

- Energy Access

- Renewable Integration

- Energy Subsidies

- Energy and Water

- Net zero emission

- Energy Security

- Critical Minerals

- A-B

- petroleum

- Mine scale

- Sewage treatment

- cement

- architecture

- Industrial information

- New energy

- Automobile market

- electricity

- Construction site

- HIMA

- ABB

- Rockwell

- Schneider Modicon

- Siemens

- xYCOM

- Yaskawa

- Woodward

- BOSCH Rexroth

- MOOG

- General Electric

- American NI

- Rolls-Royce

- CTI

- Honeywell

- EMERSON

- MAN

- GE

- TRICONEX

- Control Wave

- ALSTOM

- AMAT

- STUDER

- KONGSBERG

- MOTOROLA

- DANAHER MOTION

- Bentley

- Galil

- EATON

- MOLEX

- Triconex

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- KOLLMORGEN

- Beijer

- Endress+Hauser

- schneider

- Foxboro

- KB

- REXROTH

- YAMAHA

- Johnson

- Westinghouse

- WAGO

- TOSHIBA

- TEKTRONIX

- BENDER

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- XP POWER

- Baldor

- Meggitt

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- IBA

-

ABB PFSA240 Roll DC Supply Unit 3BSE073476R1 Industrial Stressometer Power Supply Module for Rolling Mill Systems

-

ABB PFSA107-Z42 DTU Stressometer Digital Transmission Unit High Precision Strip Tension Measurement Module

-

GE AT868-2-1-1 Ultrasonic Flow Transmitter AquaTrans AT868 Dual Channel Industrial Flow Meter

-

ABB SCC-C 23070-0-10232110 Industrial Control Module Automation System Communication Controller

-

APPLIED MATERIALS 0041-96185 - Heater Assy with 0150-45776 0190-60492 AMAT

-

APPLIED MATERIALS 0021-33426 - SHIELD INNER SINGLE 300MM NO COIL AMAT

-

APPLIED MATERIALS 0140-01905 - HARNESS ASSY DUAL IHC PRESS CONT ADAPTER 16798 AMAT

-

APPLIED MATERIALS 0051-01848 - LINE VAC EXHAUST CH Y LEAK CHECK PORT EPI AMAT

-

APPLIED MATERIALS 0010-02863 - P5000 150mm Teos Susceptor AMAT

-

APPLIED MATERIALS 0010-14056 - ASSY INJECT NOZZLE STANDARD AMAT

-

APPLIED MATERIALS 0020-34694 - LINER GDP R2 OXIDEGECO AMAT

-

APPLIED MATERIALS 0195-07416 - SYCAMORE-X CMP POLISHER I/O ASSEMBLY AMAT

-

APPLIED MATERIALS 0200-09036 - WAFER LIFT PIN AMAT

-

APPLIED MATERIALS 0021-39090 - FLANGE 10" CONFLAT ADAPTOR AMAT

-

APPLIED MATERIALS 0100-99011 - GAS INTERLOCK AMAT

-

APPLIED MATERIALS 0100-11002 - digital I/O card AMAT

-

APPLIED MATERIALS 0190-40000 - PNEUMATIC MANIFOLD CHAMBER 32903 AMAT

-

APPLIED MATERIALS 0021-39792 - PERF PLATE OX. 200 MM TEOS 21896 AMAT

-

APPLIED MATERIALS 0040-04896 - BELL JAR QUARTZ Q-KOTE 200MM AMAT

-

APPLIED MATERIALS 0020-20653 - BASE HEATER AMAT

-

APPLIED MATERIALS 0190-75057 - Lift Cylinder Assy AMAT

-

APPLIED MATERIALS 0010-70345 - Applied Materials 0042-01927

-

APPLIED MATERIALS 0100-91024 - PWBA PRE-ACCEL VENDOR I/F PCB 9500 IMPLANT AMAT

-

APPLIED MATERIALS 0041-56144 - HEATER PEDESTAL ASSEMBLY ENP FCVD EDGE AMAT

-

APPLIED MATERIALS 0090-00836 - SOURCE MOTOR ASSY 0040-24074 GFB5G10 FBLM5120W AMAT

-

MKS 0190-63631 - MASS FLOW VERIFIER MFVA-33168 AMAT

-

APPLIED MATERIALS 0100-35070 - ASSY PCB RF GENERATOR INTERFACE AMAT

-

APPLIED MATERIALS 0010-32221 - ASSEMBLY ROUGH THROTTLE VALVE DRIVE 300MM AMAT

-

SANYO DENKI 0190-14713 - P30B06040HXS8RM AC SERVO MOTOR BL SUPER AMAT

-

APPLIED MATERIALS 0190-14224 - FLEX DIST PANEL AMAT

-

APPLIED MATERIALS 0190-23897 - SPECIFICATION EXMP SYNCNET STAND ALON 14535 AMAT

-

APPLIED MATERIALS 0010-04542 - HEATER ASSY 200MM FC WXZPLUS OSCR 15607 AMAT

-

APPLIED MATERIALS 0190-51414 - AC SERVO DRIVER SGDV-OCA05AY890AA AMAT

-

APPLIED MATERIALS 0020-31747 - P5000 LOADLOCK LID WAFER TXR CHMBR 0020-32930 12573 AMAT

-

APPLIED MATERIALS 0620-01727 - CABLE ASSY SIGNAL RBN 50PIN DSUB EMI RES 17781 AMAT

-

APPLIED MATERIALS 0190-A9510 - IP POWER SUPPLY 33361 AMAT

-

APPLIED MATERIALS T1101-05-000-30 - CRYO TIGER COMPRESSOR AMAT

-

APPLIED MATERIALS 0040-13338 - LINK 1 UPPER 7.2 DEGREE OFFSET CR 300MM 38177 AMAT

-

APPLIED MATERIALS 0190-06926 - Cable SQS R/A TO SQS R/A #2 AMAT

-

APPLIED MATERIALS 0200-00705 - EDGE RING THIN 200MM AMAT

-

APPLIED MATERIALS 0190-01399 - INLINE O3 SNSR ULTRA FULL FLOW HI-CON 6627 AMAT

-

APPLIED MATERIALS 0190-21054 - RF MATCH CABLE ASSEMBLY PRECLEAN 2 AMAT

-

APPLIED MATERIALS 0041-12156 - REFLECTOR PLATE INJECT 300MM RADIANCE PLUS 29763 AMAT

-

MKS 0100-03680 - PCB CHMBR DIST 0090-09483 AS00363-16 35465 AMAT

-

APPLIED MATERIALS E11355460 - Plasma Detector E11355470 Rev.B AMAT

-

APPLIED MATERIALS 0021-33981 - LOWER SHIELD AMAT

-

APPLIED MATERIALS 0100-00583 - GAS PANEL CONTROLLER DIST AMAT

-

APPLIED MATERIALS 0010-54820 - IPC VALVE ASSEMBLY FM 1/2" INTER-PLATEN SPRAY AMAT

-

APPLIED MATERIALS 0020-31747 - P5000 LOADLOCK LID WAFER TXR CHMBR 0020-32930 12573 AMAT

-

APPLIED MATERIALS 0020-40566 - BLANK-OFF POSITION E-F ENP AMAT

-

APPLIED MATERIALS 0021-31023 - Flange Spacer Automatch Single RPS Producer SE AMAT

-

APPLIED MATERIALS 0020-21225 - WEIGHT RING 300MM TITAN PROFILER AMAT

-

APPLIED MATERIALS 0190-A9510 - IP POWER SUPPLY 33361 AMAT

-

APPLIED MATERIALS 0100-90618 - PCB H1 GROUND PDU MOTHER BOARD 0100-90036 AMAT

-

APPLIED MATERIALS 0010-04542 - HEATER ASSY 200MM FC WXZPLUS OSCR 15607 AMAT

-

APPLIED MATERIALS 0020-31658 - CLAMP VESPEL OX-MLR-NIT 200MM AMAT

-

APPLIED MATERIALS 0021-09974 - WINDOW SAPPHIRE PUMPING PLATE AMAT

-

APPLIED MATERIALS 0051-01849 - LINE VAC EXHAUST ELBOW CH Y FAC TRAY EPI 30 AMAT

-

APPLIED MATERIALS 0010-29842 - 300mm DBR High Temp Belt Wrist Titanium AMAT

-

APPLIED MATERIALS 1410-01166 - Heating Jacket AMAT

-

APPLIED MATERIALS 0620-01727 - CABLE ASSY SIGNAL RBN 50PIN DSUB EMI RES 17781 AMAT

-

APPLIED MATERIALS 0010-70345 - Applied Materials 0042-01927

-

APPLIED MATERIALS 0090-00836 - SOURCE MOTOR ASSY 0040-24074 GFB5G10 FBLM5120W AMAT

-

APPLIED MATERIALS 0190-46837 - INFRARED THERMOMETER COMM BOX RAYMI3COMM 30009 AMAT

-

APPLIED MATERIALS 0020-31886 - FLANGE INSULATION UNIBODY .400 THK AMAT

-

APPLIED MATERIALS 0010-05920 - CONTROLLER CCM PROD ETCH CS-PM CARD CAGE AMAT

-

APPLIED MATERIALS 0242-30292 - KIT 20 SCCM MFC W/HRDWR UNIBODY 6449 AMAT

-

APPLIED MATERIALS 0040-41061 - JIG FOUR PT LEVELING TOOL TXZ 300MM AMAT

-

APPLIED MATERIALS 0020-30287 - ADAPTER RING PUMPING PLATE 200MM COMMO AMAT

-

APPLIED MATERIALS 0041-12156 - REFLECTOR PLATE INJECT 300MM RADIANCE PLUS 29763 AMAT

-

APPLIED MATERIALS 0010-37866W - ASSY INT ISRM MODULE FULL SCAN SMG AMAT

-

APPLIED MATERIALS 0090-08137 - 300MM TXZ DLI HEATER CONTROLLER MODULE AMAT

-

APPLIED MATERIALS 0040-20006 - ARM WELDMENT SOURCE STD 8464 AMAT

-

APPLIED MATERIALS 0090-07392 - Dual RF filter AMAT

-

APPLIED MATERIALS 0190-06926 - Cable SQS R/A TO SQS R/A #2 AMAT

-

APPLIED MATERIALS 0020-70279 - LIFTER 150MM WAFER ORIENTER P5000 AMAT

-

APPLIED MATERIALS 0190-35652 - SERIPLEX MUX I/O PCB AMAT

-

APPLIED MATERIALS 0100-11002 - digital I/O card AMAT

-

APPLIED MATERIALS E11355460 - Plasma Detector E11355470 Rev.B AMAT

-

APPLIED MATERIALS 0010-19188 - ASSY COOLDOWN LIFT 34703 AMAT

-

APPLIED MATERIALS 0100-00975 - PCB STEPPER CONTROLLER 2 8099 AMAT

-

APPLIED MATERIALS 0190-16236 - MOTOR ENCODER ASSY ROBOT WRIST MIRRA CMP AMAT

-

APPLIED MATERIALS 0040-48671 - LEFT GUIDE 300MM L-DOOR 37961 AMAT

-

MKS 0100-03680 - PCB CHMBR DIST 0090-09483 AS00363-16 35465 AMAT

-

APPLIED MATERIALS 0190-01399 - INLINE O3 SNSR ULTRA FULL FLOW HI-CON 6627 AMAT

-

APPLIED MATERIALS 8330 - Pair Of Side viewport Panels AMAT

-

APPLIED MATERIALS 0190-75057 - Lift Cylinder Assy AMAT

-

APPLIED MATERIALS 0100-02016 - PCB ASSY ANALOG SYNC DETECT 904-125N AMAT

-

Abaco Systems 0090-08517 - VMICPCI-7326 PCB 38085 AMAT

-

APPLIED MATERIALS 0100-20069 - ASSY WAFER ORIENTER BOARD 0100-02797 AMAT

-

ELEKTRO-AUTOMATIK EA-PS 9036-070 - S01 POWER SUPPLY 625-795365 AMAT

-

APPLIED MATERIALS 3310-00139 - CAPACITANCE PIRANI GAUGE C-SEAL MOUNT 15-PIN AMAT

-

APPLIED MATERIALS 0010-00510 - ASSY BEARING STD 36806 AMAT

-

APPLIED MATERIALS 0041-13895 - FACEPLATE 26MIL CENTERHOLE RF CAP 300MM SACVD 13964 AMAT

-

APPLIED MATERIALS T1101-05-000-30 - CRYO TIGER COMPRESSOR AMAT

-

APPLIED MATERIALS 0050-10076 - WELDMENT DUAL HE MANF SACVD 20243 AMAT

-

MKS 0190-48179 - AS01294-05237-030 Hardened DeviceNet I/O Block AMAT

-

APPLIED MATERIALS 0240-75102 - 8" Transfer Blade 200mm End Effector AMAT

-

APPLIED MATERIALS 0110-90770 - Index Control PCB AMAT

-

APPLIED MATERIALS 0090-91209 - SOURCE SUPPRESSION CLAMPING BOX AMAT

-

APPLIED MATERIALS 0200-01427 - ISOLATOR CERAMIC CVD LOW K 300MM PROD AMAT

-

APPLIED MATERIALS 0021-03637 - FACEPLATE SILANE PRODUCER 200MM AMAT

-

APPLIED MATERIALS 0010-09837 - Wafer Lift Tungsten Precision 5000 AMAT

-

APPLIED MATERIALS 0101-57014 - PCB DEFLECTION-AMPLIFIER BOARD D-AMP 50-06 26296 AMAT

-

APPLIED MATERIALS 0190-36715 - PCB GP IO DISTRIBUTION AMAT

-

APPLIED MATERIALS 0660-00078 - PCB ASSY DNET ANALOG I/O CDN396 DIP-506-068 13392 AMAT

-

APPLIED MATERIALS 0190-B4670 - FIBER HARNESS DVD2-SBBI AMAT

-

APPLIED MATERIALS 1080-02356 - ACCELNET SINGLE AXIS SERVO DRIVE 800-2122 AMAT

-

APPLIED MATERIALS 0040-02937 - WATER MANIFOLD TXZ CIP 200 & 300MM AMAT

-

APPLIED MATERIALS 0040-08944 - LID ANNEAL ECP 200MM AMAT

-

SMC INOI-7134-111 - 4-PORT DEVICENET UPA MODULE Pressure Control AMAT

-

SMC INOI-7134-21 - 4-PORT DEVICENET UPA MODULE Pressure Control AMAT

-

APPLIED MATERIALS 0100-40024 - ASSY WPCBA LOADLOCK INTERCONNECT BOARD AMAT

-

APPLIED MATERIALS 0660-01635 - Chamber P2 Board A AMAT

-

APPLIED MATERIALS 0041-31945 - DOOR ENP ALUM SPD SLIT VALVE VITON LLK 3 AMAT

-

APPLIED MATERIALS 0040-48671 - LEFT GUIDE 300MM L-DOOR 37961 AMAT

-

APPLIED MATERIALS 0051-01849 - LINE VAC EXHAUST ELBOW CH Y FAC TRAY EPI 30 AMAT

-

APPLIED MATERIALS 0040-81661 - CATHODE FACILITY PLATE 35320 AMAT

-

APPLIED MATERIALS 0040-20006 - ARM WELDMENT SOURCE STD 8464 AMAT

-

APPLIED MATERIALS 0110-90770 - Index Control PCB AMAT

-

APPLIED MATERIALS 8330 - Pair Of Side viewport Panels AMAT

-

APPLIED MATERIALS 0040-81155 - LINER LOWER AMAT

-

APPLIED MATERIALS 0100-90618 - PCB H1 GROUND PDU MOTHER BOARD 0100-90036 AMAT

-

APPLIED MATERIALS 0040-47677 - FACEPLATE SIN XG DXZ DCVD AMAT

-

APPLIED MATERIALS 0020-31658 - CLAMP VESPEL OX-MLR-NIT 200MM AMAT

-

CTI-CRYOGENICS 0190-54040 - ON-BOARD IS CONTROLLER 34633 AMAT

-

APPLIED MATERIALS 0020-21665 - SHIELD AL/TI 8 INCH WAFER AMAT

-

APPLIED MATERIALS 0090-10397 - RF FILTER BOX AMAT

KONG JIANG

Add: Jimei North Road, Jimei District, Xiamen, Fujian, China

Tell:+86-15305925923