K-WANG

TEKTRONIX VX4240 VXIbus protocol waveform digitizer/analyzer module

TEKTRONIX VX4240 VXIbus protocol waveform digitizer/analyzer module

Product identity and applicable scenarios

Tektronix VX4240 is a modular waveform digitizer/analyzer based on the VXIbus protocol, designed specifically for C or D-sized VXIbus mainframes. Its core positioning is a high-precision, multifunctional signal measurement and analysis tool. It integrates a 12 bit A/D converter and RISC processor, which can be widely used in laboratory signal testing, industrial equipment monitoring, electronic system development, and other scenarios. It can complete the entire process of capturing, storing, and analyzing DC to high-frequency AC signals.

Detailed explanation of core technical parameters

1. Hardware core configuration

Specific specifications of hardware components

A/D converter with 12 bit resolution, 10 MHz sampling rate, supports high-precision conversion from analog signals to digital signals

The INMOS T800 floating-point transputer processor is responsible for signal analysis and module control

Memory configuration standard 256K word sampling memory; Optional 512K word (Option 01) or 1M word (Option 02) expansion memory

Storage module with 128K bytes of RAM (running memory) and 128K bytes of EPROM (program storage); Non volatile memory (storing calibration parameters)

Two BNC input interfaces (SIG IN+, SIG IN -) and one DB25S connector (S3) for input/output; Support TTL level triggered input/output, clock input/output, ARM input/output

2. Key parameters for signal capture

(1) Frequency and Sampling Performance

Frequency range: DC to 5 MHz, with a attenuation index of -3 dB ± 1 dB at the 5 MHz frequency point, a roll off of -6 dB/octave in the 5-10 MHz frequency band, and a roll off of -18 dB/octave in the 10-20 MHz frequency band.

Sampling frequency: Programmable range from 0.005 Hz to 10 MHz, supports three clock sources - internal clock, external clock (TTL level, 50 Ω load, DC to 10 MHz), VXIbus 10 MHz ECL clock.

Sampling interval: 100 ns to 200 s (100 ns step) in internal/external clock mode, with a minimum period of 100 ns for external clock.

Clock accuracy: The internal clock has an annual drift of 5 ppm, ensuring long-term sampling stability.

(2) Input feature configuration

Voltage range:

Calibration range: ± 0.5 V, ± 1 V, ± 2 V, ± 5 V, ± 10 V, ± 20 V, ± 50 V, ± 100 V (8 levels in total, higher accuracy).

Virtual range: Supports any non calibrated voltage range within 100V, and achieves 12 bit weight allocation through Tek's self-developed virtual range circuit, with better performance than some 14 bit digitizers.

Input type: differential input (CMRR common mode rejection ratio:>40 dB from DC to 1 kHz, typical value for 50 Ω load>50 dB, typical value for 1 M Ω load>60 dB), single ended input.

Coupling methods: AC coupling, DC coupling, and grounding are available, suitable for different signal types (such as AC coupling isolating DC components).

Input impedance:

50 Ω (± 1%, parasitic capacitance<20 pF): suitable for high-frequency signal measurement.

1 M Ω (± 3%, parasitic capacitance<20 pF): suitable for measuring low-frequency and high impedance signals.

929 k Ω (± 2%, parasitic capacitance<20 pF): Suitable only for voltage ranges of 50 V and 100 V.

Resolution (12 bits): The smaller the voltage range, the higher the resolution, such as 0.48828 mV/bit for ± 1 V range and 48.828 mV/bit for ± 100 V range.

(3) Trigger and delay control

Trigger source: Supports 5 types of trigger sources, which can be flexibly combined (AND/OR logic of any two trigger sources):

External TTL edge trigger (programmable positive/negative edge).

Dual voltage threshold triggering (± 0 to ± 100% full-scale, 8-bit resolution).

VXIbus TTL trigger (8-channel programmable trigger line selection).

The VXIbus command is triggered.

Software triggering (receiving T command to start).

Trigger mode:

Pre trigger (CP): Store data before triggering and store a specified number of samples after triggering.

Post trigger (CT): default mode, data is stored after triggering, and the default sample size is memory size -100.

Central Trigger (CC): The trigger event is located in the center of the memory, with half of the samples stored before and after.

Free Run (CF): Uncontrolled by trigger control, continuously sampling after receiving the T command until receiving the stop command.

Record mode (CR): Automatic re triggering, storing data according to the set number of samples/records, supporting up to 65534 records.

Trigger delay: Programmable range of 200 ns to 420 s (200 ns step), delay uncertainty ≤ 200 ns+1 sampling clock cycle, meeting the requirements of precise timing control.

Trigger heavy arming time: In recording mode, it is one sampling clock cycle and supports fast continuous sampling.

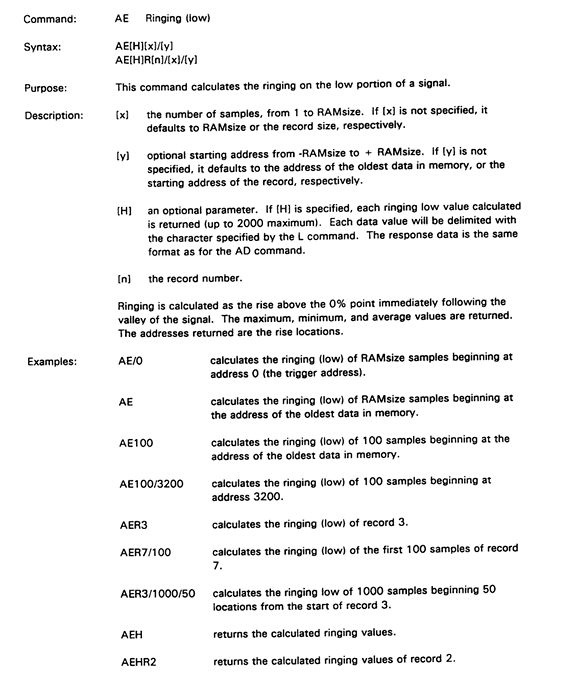

3. Signal analysis function (40+core functions)

(1) Time domain analysis function

Function Name Description

Calculate the difference between the steady-state high level (100% point) and steady-state low level (0% point) of the signal using peak to peak voltage (AK), and return the maximum/minimum/average values

Rise time (AR) measures the time it takes for a signal to rise from 10% steady state to 90% steady state, and returns the maximum/minimum/average values

Falling time (AF) measures the time it takes for a signal to drop from 90% steady state to 10% steady state, and returns the maximum/minimum/average values

Return the maximum/minimum/average value and corresponding address of the part where the overshoot (AO) signal exceeds 100% steady-state value

Return the maximum/minimum/average value and corresponding address for the part of the down rush (AU) signal below 0% steady-state value

Find the maximum/minimum voltage values and corresponding memory addresses within the specified sample range (AX/AM)

Pulse width (AW/AZ) measures the duration of pulse high/low levels, supports absolute zero or floating reference points, and returns maximum/minimum/average values

(2) Frequency domain analysis function

Function Name Description

FFT analysis (AC) fast Fourier transform, supports voltage (V) or power (dBm) units, can return maximum amplitude and frequency, harmonic parameters, etc

FFT+Hanning Window (AH) FFT with Hanning Window to reduce spectral leakage, suitable for non periodic signals

FFT+Blackman Harris Window (AQ) FFT with Blackman Harris Window, further suppressing spectral leakage and achieving higher resolution

Total Harmonic Distortion (THD) calculates the amplitude ratio of the fundamental wave to the first 5 harmonics, in dBc (relative to the carrier wave)

Signal to Noise Ratio (SNR) is the ratio of the fundamental amplitude to the amplitude of all non harmonic noise, measured in dBc

The difference between the fundamental amplitude and the maximum amplitude of the spurious signal (noise or harmonic) in the non spurious dynamic range (SFDR), measured in dBc

(3) Statistical and mathematical analysis functions

Function Name Description

Calculate the average voltage value within a specified sample range using the mean (AA)

The true RMS value (AT) calculates the true effective value of a signal (square root mean square), reflecting the actual power of the signal

The standard deviation (AS) reflects the degree of dispersion of sample data and can simultaneously return the proportion of data within the ± N σ range (N=1-9)

Integral (AI) calculation of the area under the signal curve (accumulated sample values multiplied by the sampling interval)

Differential (AD) calculates the difference between consecutive sample points, reflecting the rate of signal change

Cycle/Frequency/Duty Cycle (AY/AW/AZ) is based on zero crossing detection to calculate the signal cycle, frequency, and high-level duty cycle

(4) Recording and special analysis functions

Function Name Description

Record operation (AG) performs average, difference, and maximum/minimum value calculations on multiple records to generate new records

Single frequency DFT (AL) is a discrete Fourier transform for a specified frequency that returns amplitude (RMS) and phase (radians), supporting single/double precision

Zero crossing time (AZ) detects the zero crossing time of the signal, calculates parameters such as cycle and duty cycle, and the reference point is absolute zero

Installation and Operation Guide

1. Preparation and requirements before installation

(1) Tools and Environment

Essential tool: Phillips screwdriver.

Environmental requirements: The mainframe should provide sufficient heat dissipation (2.7 liters/second airflow, pressure drop of 0.19 mm H ₂ O, module temperature rise<10 ° C), operating temperature of 0 ° C~55 ° C, storage temperature of -40 ° C~85 ° C, relative humidity<75% (non condensing, 31 ° C~40 ° C).

(2) Switch settings (critical configuration, incorrect settings will cause module failure)

Description of switch name and position requirements

Logical address switch (S080) 1-255 (FFh is dynamically configured) base address calculation formula: [(64d × XYh)+49152d], it is recommended to match the slot number

The interrupt level switch (S081) 1-7 (0/8/9 disable interrupts) needs to match the interrupt handling level of the system controller

The Halt switch (S084) must be set to ON, otherwise the module cannot respond to VXIbus resource manager commands properly

The Bootstrap switch (S56) is set to OFF for factory testing purposes, and users do not need to adjust it

The memory size switch (S083) is preset by the factory and cannot be adjusted by oneself. It matches the hardware configuration of the memory

(3) Installation steps

Record the revised version of the module, serial number (top shield label), and switch settings, and fill in the installation checklist.

Confirm that the power supply of the host rack is turned off, and insert the module into any C/D size slot except for slot 0 (the D-size host rack should be adapted according to the host rack manual).

Tighten the module fixing screws to ensure that the front panel is grounded and avoid the risk of electric shock.

Connecting cables: The BNC interface uses RG58 coaxial cable to connect the device under test (UUT), while the DB25 interface can use CDS 73A-742P shielded connectors.

Check the overhead idle slot of the host: it needs to be covered with a blank panel to ensure heat dissipation; If there is a vacant slot on the left side of the module, the VME daisy chain jumper needs to be installed according to the host rack manual.

2. Basic operating procedures

(1) Parameter configuration (core command example)

Example Explanation of Operation Purpose Command

Set the sampling frequency F1E6 to 1 MHz (internal clock)

Configure input parameters VD5MF DC coupling, ± 5 V range, 50 Ω input impedance, differential input

Set the collection mode CR1000/50 recording mode, with 1000 samples per record and a total of 50 records

Configure trigger mode MP5.0 positive voltage threshold trigger (5.0 V)

Set the trigger delay D200E-9 to start sampling with a delay of 200 ns after triggering

(2) Sampling and analysis process

Sending configuration commands: Send parameter configuration command strings (up to 160 bytes in length, using<LF>or; Separate multiple commands.

Start sampling: Send the T (Trigger) command, the module enters the "standby" state (ARM LED lights up), and starts sampling after the triggering conditions are met (MIP LED lights up).

Data storage: Sampling data is stored in memory according to the set mode, and is automatically triggered again in recording mode until the set number of records is completed.

Signal analysis: Send A-series commands (such as AA calculating mean, AC executing FFT), and the module returns the analysis results.

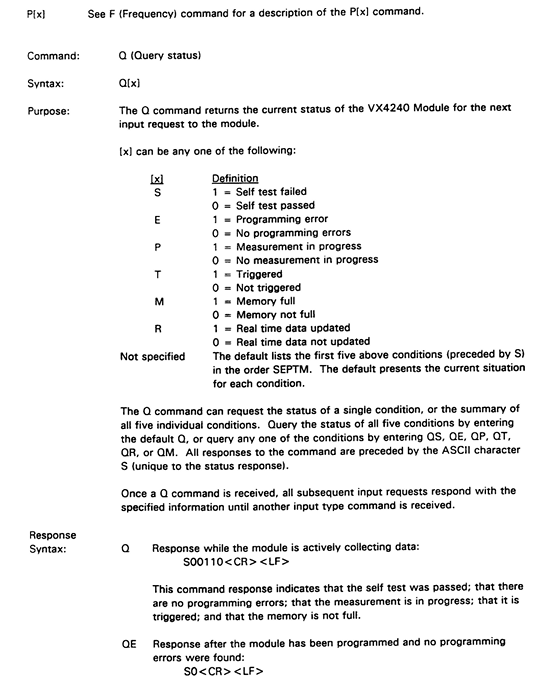

Status query and error handling:

Send Q command to query module status (self-test results, sampling progress, trigger status, etc.).

Send the E command to read the error code (such as 02 indicating CPU memory failure, 08 indicating threshold out of range). The operation can only continue after the error code is cleared.

(3) Data output

Output format: Supports ASCII, binary, complement binary, ASCII block transmission (K option, block size 1-2500).

Address control: Supports automatic address increment/decrement, and can specify the offset address relative to the trigger point (- RAMsize to+RAMsize).

Step size setting: Optional 1-65536 sampling point step size, supports interval reading of data (such as reading 1 sample every 4 samples, suitable for multiplexing scenarios).

3. Self inspection and calibration

(1) Self checking function

Power on self-test: The module is completed within 5 seconds after power on, detecting core components such as CPU memory, A/D converter, and analog front-end. If it passes, the POWER LED will remain on and the SYSFAIL LED will turn off.

Command self-test: Send the S command to initiate an extended self-test (detecting all memory, calibration parameters, trigger circuits, etc.), and return to the default power on state after completion. The results can be obtained through the Q command (querying self-test status) or the E command (reading fault error codes).

(2) Calibration requirements and operations

Calibration cycle: It is recommended to calibrate every 12 months at operating temperature, and the module should be preheated for 10 minutes before calibration.

Calibration command:

KS [range]: Simultaneously calibrate the gain and offset within a specified voltage range (results stored in non-volatile memory).

KG [range]: Only calibrate the gain.

KO [range]: Only calibrate offset.

K [range]: Software calibration, returns offset voltage (not stored, used to compensate for temperature drift).

Calibration conditions: High precision DC calibration source (accuracy 0.1%), function generator (1 MHz, accuracy 0.002%) and other equipment should be used, operated by professional personnel.

Maintenance and troubleshooting

1. Daily maintenance

Cleaning: Regularly wipe the surface of the module with a dust-free cloth to remove dust; Stubborn stains can be wiped with diluted cleaning agents, and the use of abrasive cleaning agents is prohibited.

Fuse replacement: The module is equipped with+5V, -2V, ± 24V fuses (+5V uses Littelfuse 273005 2A fast melting type, others use 273002 2A fast melting type). After the fuse is blown, the fault needs to be eliminated before replacement.

Spare parts procurement: Ordering spare parts through Tektronix local offices or distributors requires providing product model, serial number, and revised version.

2. Common troubleshooting

Troubleshooting steps for possible causes of fault phenomena

SYSFAIL LED is always on. 1. Power failure (+5V/-2V/± 24V loss); 2. Self inspection failed; 3. CPU malfunction: 1. Check if the POWER LED is turned off. If it is off, replace the fuse; 2. Send the S command to perform extended self-test, and send the E command to read error codes; 3. Contact technical support for maintenance

No sampling data (MIP LED not lit) 1. Trigger condition not met; 2. Sampling frequency/period setting error; 3. Insufficient memory 1. Check trigger mode and threshold settings (M command); 2. Verify the sampling frequency command (F/P command); 3. Reduce the sample size of a single record or expand memory

Large deviation in analysis results: 1. uncalibrated or expired calibration; 2. Incorrect input parameter settings (range, coupling, impedance); 3. Insufficient sampling frequency (not satisfying Nyquist theorem) 1. Execute KS command to calibrate the corresponding voltage range; 2. Verify the parameters of the V command (ensure they match the signal); 3. Increase the sampling frequency (at least twice the highest frequency of the signal, recommended to be more than 10 times)

Communication failure: 1. Logical address setting conflict; 2. VXIbus bus failure; 3. Command format error: 1. Reset the logical address (to avoid conflicts with other modules); 2. Check the bus connection of the host rack; 3. Ensure that the command string conforms to syntax (ASCII characters, correct delimiter)

Extension options and compatibility

1. Extension options

Option 01:512K word sampling memory expansion.

Option 02: 1M word sampling memory expansion.

Option 2A (waveform output): Supports digital signal playback, programmable delay (200 ns to 420 s), output amplitude ± 1Vpp or ± 10Vpp (50 Ω load), and needs to be used in conjunction with a waveform output card.

2. Compatibility

Host rack compatibility: Supports all C/D size host racks that comply with VXIbus specifications, and Slot 0 requires a resource manager (such as VX4521).

Interface compatibility: Supports VXIbus serial protocol, compatible with IEEE-488 (GPIB) interface (requires conversion through Slot 0 module), configurable interrupt level (1-7 levels).

Software compatibility: Provides BASIC programming language sample programs and supports mainstream measurement and control software (must follow VXIbus instrument protocol commands).

Summary of Key Appendix Information

1. Appendix Core Content

Appendix A (VXIbus Operations): Detailed explanation of module VXIbus register definition, transfer mode (normal transfer/fast handshake), and interrupt handling process.

Appendix B (I/O Connections): Provide pin definitions, signal grounding requirements, and external trigger/clock/ARM signal interface specifications for BNC and DB25 connectors.

Appendix E (Fourier Transform): Explain the FFT principle, spectral leakage suppression (window function effect), and sampling frequency selection principle (Nyquist theorem).

Appendix H (Performance Verification): Provide the verification process and equipment requirements for key indicators such as DC accuracy, AC accuracy, and Common Mode Rejection Ratio (CMRR).

Appendix I (Calibration Process): Detailed description of the operation steps and adjustment of potentiometer positions for DC gain/offset calibration, AC gain calibration, and common mode rejection calibration.

2. Important Notice

Binary transmission: When using the National Instruments GPIB-VXI/C Slot 0 module, a dedicated code instrument (CI) needs to be loaded to avoid data buffer residue.

IEEE-488 address configuration: If the GPIB address is not assigned after the system is powered on, the Slot 0 resource manager delay (set to 5 seconds) needs to be adjusted to ensure that the module completes self-test.

- YOKOGAWA

- Reliance

- ADVANCED

- SEW

- ProSoft

- WATLOW

- Kongsberg

- FANUC

- VSD

- DCS

- PLC

- man-machine

- Covid-19

- Energy and Gender

- Energy Access

- Renewable Integration

- Energy Subsidies

- Energy and Water

- Net zero emission

- Energy Security

- Critical Minerals

- A-B

- petroleum

- Mine scale

- Sewage treatment

- cement

- architecture

- Industrial information

- New energy

- Automobile market

- electricity

- Construction site

- HIMA

- ABB

- Rockwell

- Schneider Modicon

- Siemens

- xYCOM

- Yaskawa

- Woodward

- BOSCH Rexroth

- MOOG

- General Electric

- American NI

- Rolls-Royce

- CTI

- Honeywell

- EMERSON

- MAN

- GE

- TRICONEX

- Control Wave

- ALSTOM

- AMAT

- STUDER

- KONGSBERG

- MOTOROLA

- DANAHER MOTION

- Bentley

- Galil

- EATON

- MOLEX

- Triconex

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- KOLLMORGEN

- Beijer

- Endress+Hauser

- schneider

- Foxboro

- KB

- REXROTH

- YAMAHA

- Johnson

- Westinghouse

- WAGO

- TOSHIBA

- TEKTRONIX

- BENDER

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- XP POWER

- Baldor

- Meggitt

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- IBA

-

ABB PFSA240 Roll DC Supply Unit 3BSE073476R1 Industrial Stressometer Power Supply Module for Rolling Mill Systems

-

ABB PFSA107-Z42 DTU Stressometer Digital Transmission Unit High Precision Strip Tension Measurement Module

-

GE AT868-2-1-1 Ultrasonic Flow Transmitter AquaTrans AT868 Dual Channel Industrial Flow Meter

-

ABB SCC-C 23070-0-10232110 Industrial Control Module Automation System Communication Controller

-

APPLIED MATERIALS 0041-96185 - Heater Assy with 0150-45776 0190-60492 AMAT

-

APPLIED MATERIALS 0021-33426 - SHIELD INNER SINGLE 300MM NO COIL AMAT

-

APPLIED MATERIALS 0140-01905 - HARNESS ASSY DUAL IHC PRESS CONT ADAPTER 16798 AMAT

-

APPLIED MATERIALS 0051-01848 - LINE VAC EXHAUST CH Y LEAK CHECK PORT EPI AMAT

-

APPLIED MATERIALS 0010-02863 - P5000 150mm Teos Susceptor AMAT

-

APPLIED MATERIALS 0010-14056 - ASSY INJECT NOZZLE STANDARD AMAT

-

APPLIED MATERIALS 0020-34694 - LINER GDP R2 OXIDEGECO AMAT

-

APPLIED MATERIALS 0195-07416 - SYCAMORE-X CMP POLISHER I/O ASSEMBLY AMAT

-

APPLIED MATERIALS 0200-09036 - WAFER LIFT PIN AMAT

-

APPLIED MATERIALS 0021-39090 - FLANGE 10" CONFLAT ADAPTOR AMAT

-

APPLIED MATERIALS 0100-99011 - GAS INTERLOCK AMAT

-

APPLIED MATERIALS 0100-11002 - digital I/O card AMAT

-

APPLIED MATERIALS 0190-40000 - PNEUMATIC MANIFOLD CHAMBER 32903 AMAT

-

APPLIED MATERIALS 0021-39792 - PERF PLATE OX. 200 MM TEOS 21896 AMAT

-

APPLIED MATERIALS 0040-04896 - BELL JAR QUARTZ Q-KOTE 200MM AMAT

-

APPLIED MATERIALS 0020-20653 - BASE HEATER AMAT

-

APPLIED MATERIALS 0190-75057 - Lift Cylinder Assy AMAT

-

APPLIED MATERIALS 0010-70345 - Applied Materials 0042-01927

-

APPLIED MATERIALS 0100-91024 - PWBA PRE-ACCEL VENDOR I/F PCB 9500 IMPLANT AMAT

-

APPLIED MATERIALS 0041-56144 - HEATER PEDESTAL ASSEMBLY ENP FCVD EDGE AMAT

-

APPLIED MATERIALS 0090-00836 - SOURCE MOTOR ASSY 0040-24074 GFB5G10 FBLM5120W AMAT

-

MKS 0190-63631 - MASS FLOW VERIFIER MFVA-33168 AMAT

-

APPLIED MATERIALS 0100-35070 - ASSY PCB RF GENERATOR INTERFACE AMAT

-

APPLIED MATERIALS 0010-32221 - ASSEMBLY ROUGH THROTTLE VALVE DRIVE 300MM AMAT

-

SANYO DENKI 0190-14713 - P30B06040HXS8RM AC SERVO MOTOR BL SUPER AMAT

-

APPLIED MATERIALS 0190-14224 - FLEX DIST PANEL AMAT

-

APPLIED MATERIALS 0190-23897 - SPECIFICATION EXMP SYNCNET STAND ALON 14535 AMAT

-

APPLIED MATERIALS 0010-04542 - HEATER ASSY 200MM FC WXZPLUS OSCR 15607 AMAT

-

APPLIED MATERIALS 0190-51414 - AC SERVO DRIVER SGDV-OCA05AY890AA AMAT

-

APPLIED MATERIALS 0020-31747 - P5000 LOADLOCK LID WAFER TXR CHMBR 0020-32930 12573 AMAT

-

APPLIED MATERIALS 0620-01727 - CABLE ASSY SIGNAL RBN 50PIN DSUB EMI RES 17781 AMAT

-

APPLIED MATERIALS 0190-A9510 - IP POWER SUPPLY 33361 AMAT

-

APPLIED MATERIALS T1101-05-000-30 - CRYO TIGER COMPRESSOR AMAT

-

APPLIED MATERIALS 0040-13338 - LINK 1 UPPER 7.2 DEGREE OFFSET CR 300MM 38177 AMAT

-

APPLIED MATERIALS 0190-06926 - Cable SQS R/A TO SQS R/A #2 AMAT

-

APPLIED MATERIALS 0200-00705 - EDGE RING THIN 200MM AMAT

-

APPLIED MATERIALS 0190-01399 - INLINE O3 SNSR ULTRA FULL FLOW HI-CON 6627 AMAT

-

APPLIED MATERIALS 0190-21054 - RF MATCH CABLE ASSEMBLY PRECLEAN 2 AMAT

-

APPLIED MATERIALS 0041-12156 - REFLECTOR PLATE INJECT 300MM RADIANCE PLUS 29763 AMAT

-

MKS 0100-03680 - PCB CHMBR DIST 0090-09483 AS00363-16 35465 AMAT

-

APPLIED MATERIALS E11355460 - Plasma Detector E11355470 Rev.B AMAT

-

APPLIED MATERIALS 0021-33981 - LOWER SHIELD AMAT

-

APPLIED MATERIALS 0100-00583 - GAS PANEL CONTROLLER DIST AMAT

-

APPLIED MATERIALS 0010-54820 - IPC VALVE ASSEMBLY FM 1/2" INTER-PLATEN SPRAY AMAT

-

APPLIED MATERIALS 0020-31747 - P5000 LOADLOCK LID WAFER TXR CHMBR 0020-32930 12573 AMAT

-

APPLIED MATERIALS 0020-40566 - BLANK-OFF POSITION E-F ENP AMAT

-

APPLIED MATERIALS 0021-31023 - Flange Spacer Automatch Single RPS Producer SE AMAT

-

APPLIED MATERIALS 0020-21225 - WEIGHT RING 300MM TITAN PROFILER AMAT

-

APPLIED MATERIALS 0190-A9510 - IP POWER SUPPLY 33361 AMAT

-

APPLIED MATERIALS 0100-90618 - PCB H1 GROUND PDU MOTHER BOARD 0100-90036 AMAT

-

APPLIED MATERIALS 0010-04542 - HEATER ASSY 200MM FC WXZPLUS OSCR 15607 AMAT

-

APPLIED MATERIALS 0020-31658 - CLAMP VESPEL OX-MLR-NIT 200MM AMAT

-

APPLIED MATERIALS 0021-09974 - WINDOW SAPPHIRE PUMPING PLATE AMAT

-

APPLIED MATERIALS 0051-01849 - LINE VAC EXHAUST ELBOW CH Y FAC TRAY EPI 30 AMAT

-

APPLIED MATERIALS 0010-29842 - 300mm DBR High Temp Belt Wrist Titanium AMAT

-

APPLIED MATERIALS 1410-01166 - Heating Jacket AMAT

-

APPLIED MATERIALS 0620-01727 - CABLE ASSY SIGNAL RBN 50PIN DSUB EMI RES 17781 AMAT

-

APPLIED MATERIALS 0010-70345 - Applied Materials 0042-01927

-

APPLIED MATERIALS 0090-00836 - SOURCE MOTOR ASSY 0040-24074 GFB5G10 FBLM5120W AMAT

-

APPLIED MATERIALS 0190-46837 - INFRARED THERMOMETER COMM BOX RAYMI3COMM 30009 AMAT

-

APPLIED MATERIALS 0020-31886 - FLANGE INSULATION UNIBODY .400 THK AMAT

-

APPLIED MATERIALS 0010-05920 - CONTROLLER CCM PROD ETCH CS-PM CARD CAGE AMAT

-

APPLIED MATERIALS 0242-30292 - KIT 20 SCCM MFC W/HRDWR UNIBODY 6449 AMAT

-

APPLIED MATERIALS 0040-41061 - JIG FOUR PT LEVELING TOOL TXZ 300MM AMAT

-

APPLIED MATERIALS 0020-30287 - ADAPTER RING PUMPING PLATE 200MM COMMO AMAT

-

APPLIED MATERIALS 0041-12156 - REFLECTOR PLATE INJECT 300MM RADIANCE PLUS 29763 AMAT

-

APPLIED MATERIALS 0010-37866W - ASSY INT ISRM MODULE FULL SCAN SMG AMAT

-

APPLIED MATERIALS 0090-08137 - 300MM TXZ DLI HEATER CONTROLLER MODULE AMAT

-

APPLIED MATERIALS 0040-20006 - ARM WELDMENT SOURCE STD 8464 AMAT

-

APPLIED MATERIALS 0090-07392 - Dual RF filter AMAT

-

APPLIED MATERIALS 0190-06926 - Cable SQS R/A TO SQS R/A #2 AMAT

-

APPLIED MATERIALS 0020-70279 - LIFTER 150MM WAFER ORIENTER P5000 AMAT

-

APPLIED MATERIALS 0190-35652 - SERIPLEX MUX I/O PCB AMAT

-

APPLIED MATERIALS 0100-11002 - digital I/O card AMAT

-

APPLIED MATERIALS E11355460 - Plasma Detector E11355470 Rev.B AMAT

-

APPLIED MATERIALS 0010-19188 - ASSY COOLDOWN LIFT 34703 AMAT

-

APPLIED MATERIALS 0100-00975 - PCB STEPPER CONTROLLER 2 8099 AMAT

-

APPLIED MATERIALS 0190-16236 - MOTOR ENCODER ASSY ROBOT WRIST MIRRA CMP AMAT

-

APPLIED MATERIALS 0040-48671 - LEFT GUIDE 300MM L-DOOR 37961 AMAT

-

MKS 0100-03680 - PCB CHMBR DIST 0090-09483 AS00363-16 35465 AMAT

-

APPLIED MATERIALS 0190-01399 - INLINE O3 SNSR ULTRA FULL FLOW HI-CON 6627 AMAT

-

APPLIED MATERIALS 8330 - Pair Of Side viewport Panels AMAT

-

APPLIED MATERIALS 0190-75057 - Lift Cylinder Assy AMAT

-

APPLIED MATERIALS 0100-02016 - PCB ASSY ANALOG SYNC DETECT 904-125N AMAT

-

Abaco Systems 0090-08517 - VMICPCI-7326 PCB 38085 AMAT

-

APPLIED MATERIALS 0100-20069 - ASSY WAFER ORIENTER BOARD 0100-02797 AMAT

-

ELEKTRO-AUTOMATIK EA-PS 9036-070 - S01 POWER SUPPLY 625-795365 AMAT

-

APPLIED MATERIALS 3310-00139 - CAPACITANCE PIRANI GAUGE C-SEAL MOUNT 15-PIN AMAT

-

APPLIED MATERIALS 0010-00510 - ASSY BEARING STD 36806 AMAT

-

APPLIED MATERIALS 0041-13895 - FACEPLATE 26MIL CENTERHOLE RF CAP 300MM SACVD 13964 AMAT

-

APPLIED MATERIALS T1101-05-000-30 - CRYO TIGER COMPRESSOR AMAT

-

APPLIED MATERIALS 0050-10076 - WELDMENT DUAL HE MANF SACVD 20243 AMAT

-

MKS 0190-48179 - AS01294-05237-030 Hardened DeviceNet I/O Block AMAT

-

APPLIED MATERIALS 0240-75102 - 8" Transfer Blade 200mm End Effector AMAT

-

APPLIED MATERIALS 0110-90770 - Index Control PCB AMAT

-

APPLIED MATERIALS 0090-91209 - SOURCE SUPPRESSION CLAMPING BOX AMAT

-

APPLIED MATERIALS 0200-01427 - ISOLATOR CERAMIC CVD LOW K 300MM PROD AMAT

-

APPLIED MATERIALS 0021-03637 - FACEPLATE SILANE PRODUCER 200MM AMAT

-

APPLIED MATERIALS 0010-09837 - Wafer Lift Tungsten Precision 5000 AMAT

-

APPLIED MATERIALS 0101-57014 - PCB DEFLECTION-AMPLIFIER BOARD D-AMP 50-06 26296 AMAT

-

APPLIED MATERIALS 0190-36715 - PCB GP IO DISTRIBUTION AMAT

-

APPLIED MATERIALS 0660-00078 - PCB ASSY DNET ANALOG I/O CDN396 DIP-506-068 13392 AMAT

-

APPLIED MATERIALS 0190-B4670 - FIBER HARNESS DVD2-SBBI AMAT

-

APPLIED MATERIALS 1080-02356 - ACCELNET SINGLE AXIS SERVO DRIVE 800-2122 AMAT

-

APPLIED MATERIALS 0040-02937 - WATER MANIFOLD TXZ CIP 200 & 300MM AMAT

-

APPLIED MATERIALS 0040-08944 - LID ANNEAL ECP 200MM AMAT

-

SMC INOI-7134-111 - 4-PORT DEVICENET UPA MODULE Pressure Control AMAT

-

SMC INOI-7134-21 - 4-PORT DEVICENET UPA MODULE Pressure Control AMAT

-

APPLIED MATERIALS 0100-40024 - ASSY WPCBA LOADLOCK INTERCONNECT BOARD AMAT

-

APPLIED MATERIALS 0660-01635 - Chamber P2 Board A AMAT

-

APPLIED MATERIALS 0041-31945 - DOOR ENP ALUM SPD SLIT VALVE VITON LLK 3 AMAT

-

APPLIED MATERIALS 0040-48671 - LEFT GUIDE 300MM L-DOOR 37961 AMAT

-

APPLIED MATERIALS 0051-01849 - LINE VAC EXHAUST ELBOW CH Y FAC TRAY EPI 30 AMAT

-

APPLIED MATERIALS 0040-81661 - CATHODE FACILITY PLATE 35320 AMAT

-

APPLIED MATERIALS 0040-20006 - ARM WELDMENT SOURCE STD 8464 AMAT

-

APPLIED MATERIALS 0110-90770 - Index Control PCB AMAT

-

APPLIED MATERIALS 8330 - Pair Of Side viewport Panels AMAT

-

APPLIED MATERIALS 0040-81155 - LINER LOWER AMAT

-

APPLIED MATERIALS 0100-90618 - PCB H1 GROUND PDU MOTHER BOARD 0100-90036 AMAT

-

APPLIED MATERIALS 0040-47677 - FACEPLATE SIN XG DXZ DCVD AMAT

-

APPLIED MATERIALS 0020-31658 - CLAMP VESPEL OX-MLR-NIT 200MM AMAT

-

CTI-CRYOGENICS 0190-54040 - ON-BOARD IS CONTROLLER 34633 AMAT

-

APPLIED MATERIALS 0020-21665 - SHIELD AL/TI 8 INCH WAFER AMAT

-

APPLIED MATERIALS 0090-10397 - RF FILTER BOX AMAT

K-JIANG

Add: Jimei North Road, Jimei District, Xiamen, Fujian, China

Tell:+86-15305925923